| 电路设计 单片机学习 PCB设计 电子制作 电工基础 电路基础 电子电路图 电脑技术 维修教程 手机数码 家电维修 电力技术 电气技术 |

| 电子基础 arm嵌入式 集成电路 模拟电子 电源管理 显示光电 楼宇控制 安防监控 控制电路 音响功放 单元电路 电子下载 维修资料下载 |

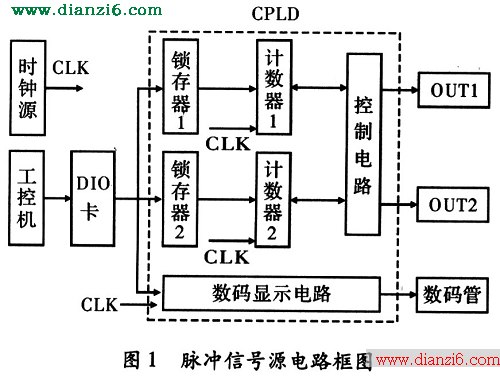

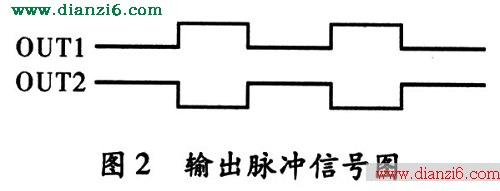

时钟电路采用80 MHz有源晶振,它为系统提供时钟信号;锁存器1及锁存器2用于保存频率及占空比数据,为16位计数器提供预置值,锁存器位数为8位,设定的数据通过工控机输入,由于计数器位数为16位,故需分两次打人数据;计数器1及计数器2作为定时器,按锁存器1、2设定的值计时,两个计数器交替工作,即一个计数器工作而另一个计数器不工作。当工作的计数器到达计时时间后,向控制电路发出时间到信号。控制电路接收计数器发出的信号,停止计数器工作,并重新装载计时数据,同时启动另一个计数器工作,从而产生规定频率、占空比的脉冲信号,并输出两路脉冲信号,如图2所示。为了提高信号源带负载能力,输出使用了7417367驱动芯片增加驱动电流。

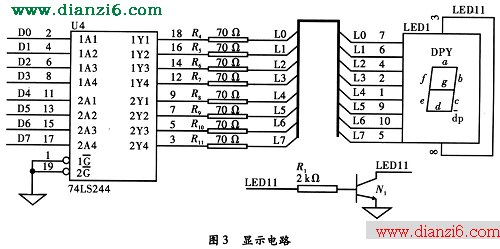

显示电路图,如图4所示,其中需要显示的数据代码通过工控机输入。缓冲器74LS244用做多路开关,当选通信号有效时,该路锁存数据有效,数码管显示相应的数据。

频率及占空比数据按如下方式计算:

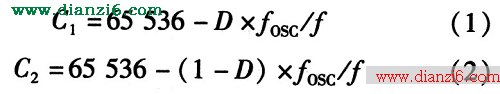

设要输出的频率为f,占空比为D,则锁存器1、2要设定的值分别为

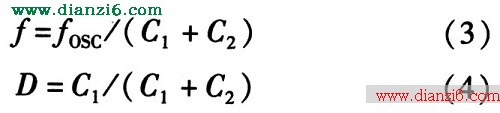

其中fOSC为系统时钟,C1、C2采用2进制补码。由式(1),式(2)式可得到频率及占空比计算式

由上式可以看出信号源最高输出频率取决于系统时钟频率,最高频率为系统时钟频率的一半(C1、C2均为1),要提高信号源输出频率必须提高系统时钟频率,既采用高频晶振或倍频电路。占空比取决于C1与C1+C2的比值,输出频率为最高频率时,占空比为50%;同样最小步进也取决于系统时钟频率,提高系统时钟频率,就可使步进缩小。

如果要信号源输出频率为500 kHz,占空比为0.5的脉冲波,则按式(1)、式(2)可以算出,C1=C2=HB0(16进制数)。将C1、C2通过工控机置入CPLD中。如果C1、C2为小数,则需取整,取整后需按式(3)、式(4)重新计算频率和占空比,算出的值为实际的频率与占空比。

2 硬件编程

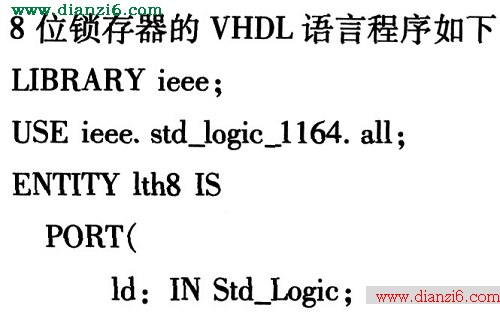

开发软件采用Max PlusⅡ10.2,编程采用VHlDL硬件描述语言。

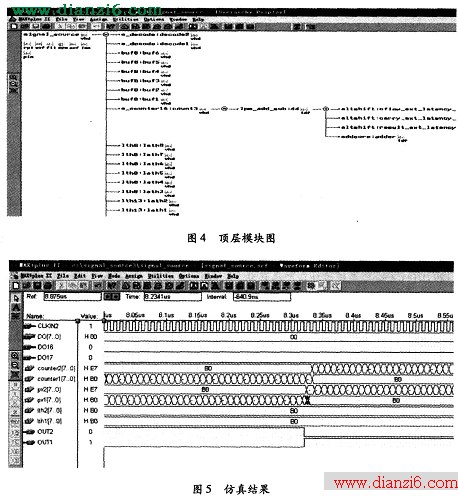

编程采用层次结构,整个程序采用顶层模块和底层模块。顶层模块,如图4所示。底层模块包括系统包含的各组件。

整个程序编写完成后进行编译、仿真,仿真结果,如图5所示。编译、仿真通过后都正确,即可通过JTAG接口将程序下载到目标板CPLD中,目标板即可使用。

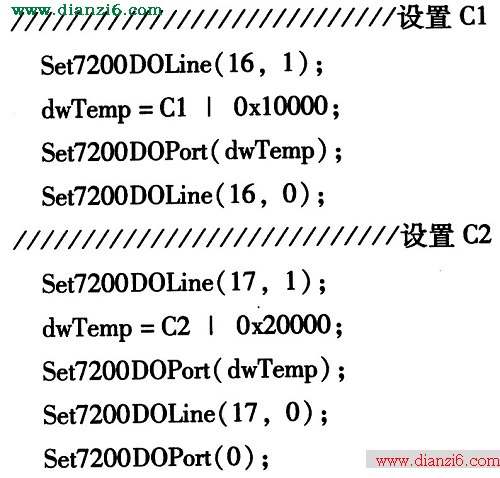

3 系统控制软件

系统控制软件采用LabWindows/CVI编写,为了给锁存器置数,可采用如下程序实现:

4 技术指标

本脉冲信号源输出脉冲频率:20~700 kHz,占空比:1%~40%,时钟采用80 MHz有源晶振。在700 kHz时频率步进为6 kHz,20 kHz时频率步进为5 Hz。

由于采用了EPM7128SLC84—10作为脉冲信号源的核心。电路结构简单,频率、占空比可任意设置,准确度高。同时操作简单方便,功能更易扩展。

温馨提示; 本站的资料全部免费下载,为方便下次找到本站记得将本站加入收藏夹哦,牢记网址http://www.dianzi6.com

温馨提示; 本站的资料全部免费下载,为方便下次找到本站记得将本站加入收藏夹哦,牢记网址http://www.dianzi6.com|

此页提供单片机脉冲信号源的CPLD实现方案单片机开发,单片机原理,单片机教程, 单片机学习参考。本站还有更多的单片机学习相关资料分享。

Copyright© www.dianzi6.com Inc. All rights reserved 。 1 2 3 4 5 6 7 8 |

|