| 电路设计 单片机学习 PCB设计 电子制作 电工基础 电路基础 电子电路图 电脑技术 维修教程 手机数码 家电维修 电力技术 电气技术 |

| 电子基础 arm嵌入式 集成电路 模拟电子 电源管理 显示光电 楼宇控制 安防监控 控制电路 音响功放 单元电路 电子下载 维修资料下载 |

1.集成数值比较器得功能

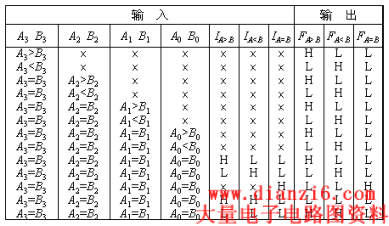

集成数值比较器74LS85是4位数值比较器,其功能如下:

从功能表可以看出,该比较器的比较原理和两位比较器的比较原理相同。两个4位数的比较是从A的最高位A3和B的最高位B3进行比较,如果它们不相等,则该位的比较结果可以作为两数的比较结果。若最高位A3=B3,则再比较次高位A2和B2,余类推。显然,如果两数

相等,那么,比较步骤必须进行到最低位才能得到结果。

真值表中的输入变量包括A3与B3、A2与B2、A1与B1、A0与B0和A与B的比较结果。其中A和B是另外两个低位数,IA>B、IA<B和IA=B是它们的比较结果。设置低位数比较结果输入端是为了能与其他数值比较器连接,以便组成位数更多的数值比较器。根据1位数值比较器逻辑表达式可知:

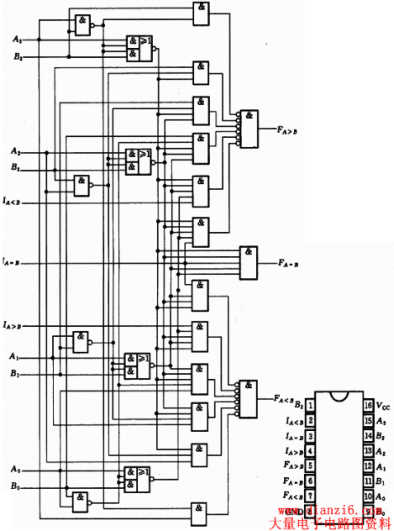

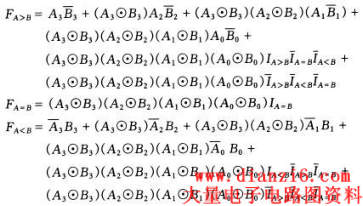

再根据74LS85的功能表可得:

上式与逻辑图一致。由上式可以看出,仅对4位数进行比较时,应对IA>B、IA<B和IA=B进行适当处理,即IA>B=IA<B=0,IA=B=1。

2.数值比较器的位数扩展

现在来讨论一下数值比较器的位数扩展问题。数值比较器的扩展方式有串联和并联两种。

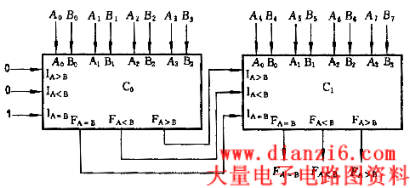

下图表示两个4位数值比较器串联而成为一个8位数值比较器。

我们知道,对于两个8位数,若高4位相同,它们的大小则由低4位的比较结果确定。因此,低4位的比较结果应作为高4位的条件

,即低4位比较器的输出端应分别与高4位比较器的IA>B、IA<B、IA=B端连接。

当位数较多且要满足一定的速度要求时,可以采取并联方式。

下图表示16位并联数值比较器的原理图。

由图可以看出,这里采用两级比较方法,将16位按高低位次序分成4组,每组4位,各组的比较是并行进行的。将每组的比较结果再经4位比较器进行比较后得出结果。显然,从数据输入到稳定输出只需两倍的4位比较器延迟时间,若用串联方式,则16位的数值比较器从输入到稳定输出需要4倍的4位比较器的延迟时间。

|

此页提供集成数值比较器电子电路基础,模拟电路基础, 电路基础参考。本站还有更多的电路基础相关资料分享。

Copyright© www.dianzi6.com Inc. All rights reserved 。 1 2 3 4 5 6 7 8 |

|