| 电路设计 单片机学习 PCB设计 电子制作 电工基础 电路基础 电子电路图 电脑技术 维修教程 手机数码 家电维修 电力技术 电气技术 |

| 电子基础 arm嵌入式 集成电路 模拟电子 电源管理 显示光电 楼宇控制 安防监控 控制电路 音响功放 单元电路 电子下载 维修资料下载 |

摘要:结合高速FPGA的特点, 设计了一套数据采集系统。该系统以FPGA作为采集系统的核心, 应用FPGA的内部逻辑实现时序控制,对数据进行采集、显示,并将处理后的结果通过USB口传输到上位机。该系统具有电路结构简单、功耗低等优点, 可用于温度、压力等传感器信息以及电压、电流的数据采集。

1 引言

在科学技术研究和工业生产的各行业中, 常常需要对各种数据进行采集, 如液位、温度、 压力、频率等信息的采集。随着数字技术的发展, 一些高性能的FPGA (Field Programmable Gate Array)和高速的A/D 应用于数据采集系统中, 大大提高了系统的测量精度、数据采集处 理速度、数据传输速度等。本文设计了一种应用EP1K10TC100 FPGA 和单片机的数据采集 系统。该系统具有数据采集速度高、功耗低、数据传输方便等优点。

2 设计设计

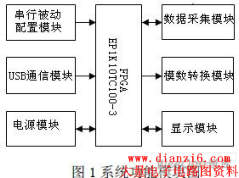

基于 FPGA 的数据采集系统的总体功能模块如下图1 所示。系统有由FPGA、串行被动 配置模块、USB 通信模块、电源模块、显示模块、模数转换模块、数模转换模块等几个模 块组成。

主控芯片采用ACEX1K 系列的EP1K10TC100-3。ACEX 系列是当今Altera CPLD 中应 用前景最好的器件系列之一[1,2],该系列的FPGA 由逻辑阵列块LAB(Logic array block)、 嵌入式阵列块EAB(embedded array block)、快速互联以及IO 单元构成,每个逻辑阵列块 包含8 个逻辑单元LE(logic element)和一个局部互联。每个逻辑单元则由一个4 输入查找 表(LUT)、一个可编程触发器、快速进位链、级连链组成,多个LAB 和多个EAB 则可通过快速通道互相连接[3]。EAB 是ACEX 系列器件在结构设计上的一个重要部件,他是输入 端口和输出端口都带有触发器的一种灵活的RAM 块,其主要功能是实现一些规模不太大的 FIFO、ROM、RAM 和双端口RAM 等。

3 系统硬件设计与实现

3.1 数据采集模块

系统数据采集采用DAC0832。ADC0832 是美国国家半导体公司生产的一种8 位分辨 率、双通道A/D 转换芯片,最高分辨可达256 级,可以适应一般的模拟量转换要求。其内 部电源输入与参考电压的复用,使得芯片的模拟电压输入在0~5V 之间。芯片转换时间仅为 32μS,据有双数据输出可作为数据校验,以减少数据误差,转换速度快且稳定性能强。独 立的芯片使能输入,使多器件挂接和处理器控制变的更加方便。通过控制数据输入端,可以 轻易的实现通道功能的选择。

FPGA 的 I/O 口直接与DAC0832 连接[4],通过VHDL 语言配置FPGA 芯片,以达到对 DAC0832 数模转换的时序控制。ADC0809 与FPGA 的连接电路比较简单,只要把控制引脚 和数据输出引脚连接到 I/O 口上。

3.2 串行被动配置模块

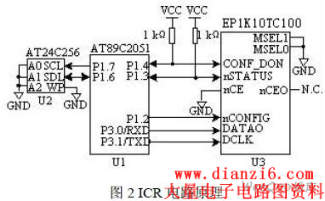

因为基于SRAM 工艺FPGA 存在掉电易失性特点,所以配置模块的主要是在每次上电 后对FPGA 进行重新配置[4]。编程文件可以放在通用程序存储器中, 在FLEX 器件上电后, 由芯片外部控制器自动地从通用存储器中读出编程文件并送到FLEX 器件进行配置, 数据传 送方式可以为串行,也可以为并行。被动串行(PS)配置模式的配置接口连接到芯片的5 个 引脚,分别为:nSTATUS、nCONFIG、CONF_DONE、DCLK、DATA0。 ICR 电路原理如图2 所示。

ICR 控制电路的工作过程为:经MAXPLUS II 编译生产的配置文件(.sof)通过格式转换 成为 (.rbf)。然后,通过PC 机的串行通信口,经AT89C2051 单片机控制存储在AT24C256 中。单片机再根据系统的要求,通过P1.2、P1.3、P1.4、P3.0 和P3.1 等5 个I/O 口,将其存 储在AT24C256 中的配置数据下载到电路中的FPGA 器件中去。

3.3 USB 通信模块

USB 接口芯片采用ISP1581。该芯片全面符合USB2.0 规范,具有高速的并行通用接 口,可在高速模式下工作,理论最高传输速度达到480Mbps[5]。除了控制端点外,ISP1581 还 有7 个输入( IN) 端点和7 个输出( OUT)端点。每个端点可以灵活配置数据传输方式以及数 据缓存区( FIFO) 的大小, 端点FIFO 最大容量可以达到2KB。ISP1581 芯片在配置枚举时 需要单片机固件的支持, 一旦正确完成了配置和驱动加载, 单片机对于ISP1581 芯片就如同 普通存储器一样可以进行读写操作, 以发送或接收数据。

3.4 显示模块

LED 采用四位共阳极数码管显示。共阳极四位一体数码管采用动态扫描工作方式,在 数码管中每一位的字段位a、b、c、d、e、f、g 和dp 分别连接在一起,其工作原理与共阴 极数码管工作原理一致,只不过共阳极输入数码管的发光电平(有效电平)是0,和共阴极 数码管相反。在数码管显示电路中运用了一个驱动芯片74LS47,运用这个驱动主要解决如 下几个问题:(1)电平正负转换,(2)译码,可以节约I/O 口的占用。74 LS47 接受四位BCD 码输入,并通过7 个与/或门译码后输出,用于驱动数码管,其输出的低电平驱动共阳极数 码管,低电平输出电流在24mA 以上。

3.5 电源模块

该设计中内核电压和I/O 口电压都采用2.5V.因为该芯片对电源要求很严格,所以通过 稳压块来实现电源转换。在该电路中通过一片1117-2.5 稳压块由5V 转化而来。电路连接便 捷简单,输出电流可以达到1A,基本上能满足该系统的需求。

4 被动串行配置程序设计

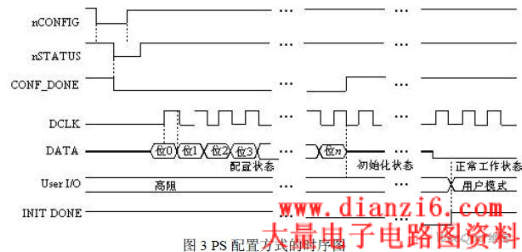

PS 配置方式的时序图如图3 所示。

配置前必须先设置该芯片EP1K10TC100-3 上的下载模式选择引脚MSEL1、MSEL0。 设置方式:当MSEL1=0,MSEL0=0 时系统为PS 或AS 模式当MSEL1=1, MSEL0=0 时系统为PPS 模式,当MSEL1=1,MSEL0=1 时系统为PPA 模式。在这里设置成使MSEL1 =0、MSEL0=0 在PS 配置过程中:当nCONFIG 产生下降沿脉冲时启动配置过程,在DCLK 上升沿, 将数据移入目标芯片中。

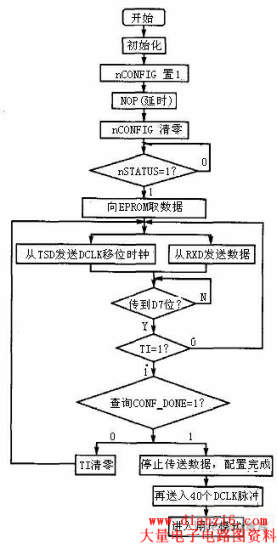

在配置过程中,系统需要实时监测,一旦出错,nSTATUS 将被拉 低,系统识别到这个信号后,立即重新启动配置过程。配置数据全部正确地移入目标芯片内 部后,CONF_DONE 信号跳变为高,此后,DCLK 必须提供几个周期的时钟(具体周期数 与DCLK 的频率有关),确保目标芯片被正确初始化,进入用户工作模式。配置流程图如图 4 所示:

图4 被动串行配置流程图

5 总结:

本文创新点: 系统采用ACEX1K 系列的EP1K10TC100-3 FPGA 作为控制和处理的核心, 简化了系统的硬件设计, 具有功耗低、速度快等优点;采用基于微控制器的FPGA 器件的 ICR 控制系统,具有线路结构简单、开发容易、体积小、成本低的优点;采用USB 与上位 机通信,代替传统的串口数据传输, 提高了数据传输速率和可扩展性,而且USB 可以总线 供电,在数据采集系统中耗电量小。

温馨提示; 本站的资料全部免费下载,为方便下次找到本站记得将本站加入收藏夹哦,牢记网址http://www.dianzi6.com

温馨提示; 本站的资料全部免费下载,为方便下次找到本站记得将本站加入收藏夹哦,牢记网址http://www.dianzi6.com|

此页提供基于FPGA 的数据采集系统设计eda技术,eda技术实用教程, EDA/PLD参考。本站还有更多的EDA/PLD相关资料分享。

Copyright© www.dianzi6.com Inc. All rights reserved 。 1 2 3 4 5 6 7 8 |

|