| 电路设计 单片机学习 PCB设计 电子制作 电工基础 电路基础 电子电路图 电脑技术 维修教程 手机数码 家电维修 电力技术 电气技术 |

| 电子基础 arm嵌入式 集成电路 模拟电子 电源管理 显示光电 楼宇控制 安防监控 控制电路 音响功放 单元电路 电子下载 维修资料下载 |

摘要:本文描述了一个基于可编程逻辑器件的全彩LED显示系统的设计的过程,这个系统能够基于硬件产生LED更多颜色灰度。详细分析了其工作原理,并依据其原理,设计出了基于FPGA 的控制电路。

1 引言

LED 的发展已过了几十年了,它现在的技术也相当成熟了。它有很宽的可视角,并且能够 显示图像、数字、视频,还能够通过红绿篮三种LED 组合成任一颜色系统,但是不推荐在 小显示屏上显示视频。典型应用是在商场、高速公路、大型体育场和白天日照下的舞台[1]。

我们都知道,由PN 结构成的LED 需要用直流电源驱动发出其颜色,改变通过PN 结上 的电流达到显示颜色亮度的变化。每个显示板上的LED 都是被恒流源产生的可控电流单独 直接控制,虽然一个LED 颜色灰度容易产生,但是大量LED 组成的LED 显示屏就需要一个 非常复杂的控制系统来控制。本文的目的是实现这个基于FPGA 的具有高刷新率的全彩LED 显示控制系统。本文介绍了LED 显示系统中三基色发光管同时产生灰度的工作原理,也描述 了基于FPGA 的 LED 显示系统模型在细节上的实现[2]。

2 LED 显示面板的工作原理

根据驱动 LED 的工作原理LED 显示屏有静态、虚拟、扫描之分,那么对应的LED 显示控制系统也不同。本文介绍的是适合扫描屏的LED 控制系统。

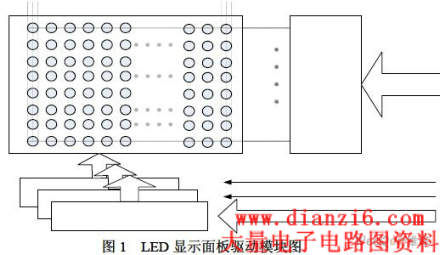

目前,许多LED 显示面阵板是利用8*8 的LED 矩阵块拼接起来,这有益于PCB 的设 计和节省空间,在本文的研究中就是使用这样的LED 面阵板[3]。如图1 所示,由8 块8*8 的矩阵块组成,三色LED 点阵利用每行的阴极作为公共端,行的选通是通过3-8 译码器驱 动NPN 三极管来控制的,并且任一时刻只有一行被Ri 选通;每列有3 路输入信号Rc、Gc、 Bc 分别单独控制每列的红、绿、蓝LED,每种颜色有8 个8 位移位寄存器(74HC595)提 供恒流去控制列。为了便于读图,在图中没画出LED 和驱动芯片间的限流电阻。

很明显,能得到的颜色值仅仅是红、绿、蓝三种颜色组成的,颜色灰度实际上是依靠改 变颜色亮度值产生的,颜色亮度的控制是通过驱动LED 像素点在一周期内总的导通时间来 决定的。为了产生颜色灰度需要对LED 像素值进行重新分配,这需要在控制系统里实现对 同一位面的数据进行组合,然后发送到LED 面阵板。

3 基于可编程逻辑器件的LED 显示控制器

LED 显示屏为了获得更高的亮度等级,显示控制器必须能够在一个可接受的周期内刷 新整个LED 屏,如果这个不能达到,闪变效应就会影响观众。微处理器和微控制器在普通 的控制方面是很强的芯片,但是它不太适合控制带合适亮度等级和高刷新率的LED 显示屏。 所以使用基于可编程逻辑器件的控制器来实现是一个很好的选择 [4]。

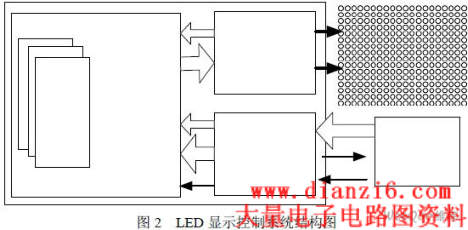

如图 2 所示的结构,LED 显示控制由器由LEDINTERFACE、BUFFERUPDATA 和 VIDEORAM 模块组成[5]。LEDINTERFACE 和BUFFERUPDATA 两个模块共用一个SRAM 存储器,它类似于一双通道存储器。以下几个部分详细说明这几个模块。

3.1 LEDINTERFACE 模块

LEDINTERFACE 模块是负责控制图1 所示的LED 点阵的颜色显示,如图3 所示为 LEDINTERFACE 模块的状态机的状态图。它能够很方便的表现状态转换和数据流动,最重 要的是一个状态图能够简单的修改成VHDL 程序。

从这图中看出,LEDINTERFACE 模块的初始化状态是INIT_SIGNALS,它初始化所有 涉及到LED 显示屏上的信号,然后准备转换到SET_PIXEL_ADDRESS 状态,这个状态计 算输出数据缓冲器中的地址(VIDEORAM 的地址),在READ_PIXEL 状态读出数据。注意, READ_PIXEL 不仅是取数据而且决定当前的LED 状态是否需要去置位或清除有关像素数据 的亮度值和当前位面。READ_PIXEL 状态利用一个PIXCOLOR 表,如表1 所示,这个表存 储的是像素颜色值和亮度的关联数据。用作重新得到LED 状态的参量是像素数据DataR、 DataG、DataB、Plane,在不增加显示缓冲区的情况下,把一个像素的颜色值直接转换成LED 的亮度等级,不仅是一个简单的方法,而且相比较以前的方法能减少硬件复杂度和存储器的 使用。

下面举一像素颜色转换的例子,说明这个方法的工作过程。例如首先位面值是‘0’,1 个点的像素值是是(4,0,2),分别是RED,GREEN,BLUE,在READ_PIXEL 期间,这 些像素值同时从VIDEORAM 中取出存到DataInR,DataInG,DataInB,再通过查表1 可以 得到,位面值为‘0’时的LED 状态(RI,GI,BI)即第PIXCOLORE 第一位(1,0,1); 位面值是‘1’时即第二位(1,0,1);位面值‘3’时即第三位(1,0,0)。很显然,32 个位面值都取完后,这个像素点的RGB 发光管在这个周期的导通时间分别是4/32,0/32, 2/32,实际上由于LED 面板是1/8 扫描的,RGB 发光管的导通时间分别是4/256,0/256, 2/256,这个过程产生了LED 的不同灰度[6]。

一旦 R、G、B 状态定下来,状态机的下两个状态ACTIVE_CLK 和INACTIVE_CLK 把 RDi、GDi、BDi 里的数据移位到LED 面板上,这些操作被重复直到当前所有LED 数据分 配完,重复次数由一个计数器控制,计数器的最大值是LED 面板每行的LED 数。

当一行所有的 LED 数据分配完成后,状态机进入OUT_ROW_BUS 状态,激活LED 显 示面板的当前行,并更新cROW 指向下一行,DELAY 状态是为了能够在退出更新状态以前, 在扫描延时的控制下使能行一段周期。多路扫描速率由SCAN_DELAY 控制,在更新行期间 (cROW=cROW+1),如果cROW 小于8,则继续回到SET_PIXEL_ADDRESS 状态开始扫描 下一行。另外,,如果8 行全部扫描完成,它将进到ADVANCE_PLANE 状态。从这个状态 图可以看出,颜色位面是32 个,总共能够显示的颜色是32*32*32=32768 色。

3.2 BUFFERUPDATA 模块

BUFFERUPDATA 模块是作视频源信号和VIDEOSRAM 的接口部分。BUFFERUPDATA 设计了只接收24 位RGB 数据格式的信号,这种格式的信号可以很容易的从标准的视频源 信号转换过来,且这种转换模块需要带数据缓冲区。

除了24 位颜色数据总线,BUFFERUPDATA 模块还增加了2 个信号:RDB_FULL 和 RGB_RD。RGB_FULL 是指示RGB 视频源缓冲区中至少有一个像素值可以读取, BUFFERUPDATA 模块去使能RGB_RD 信号,然后通过24 位数据总线去读取视频源缓冲区 中的值。如图3 所示,用有限状态机来描述这个模块。

从图 3 可以看出,这个BUFFERUPDATA 模块的初始状态是IDLE,所有有关信号都在 这个状态被初始化,并且检测RGB_FULL 信号状态;从IDLE 状态到ACF_RD 是通过 RGB-FULL 信号来激励的;在ACT_RD 和INACT_RD 状态为了得到RGB 数据强制 BUFFERUPDATA 模块产生RGB-RD 信号。RGB-RD 有效的时间是DELAY 的值来控制的, DELAY 的值是在ACD-RD 状态重复的时钟周期数。

接收完数据后,BUFFERUPDATA 模块没有立即把数据存到VIDEORAM 中,而是检查 MemBusy 信号的状态,为了保证VIDEORAM 模块可操作,即没有被LEDINTERFACE 模 块占用;当MemBusy 信号无效时,BUFFERUPDATA 模块就把得到的RGB 数据存到相应 的VIDEORAM 地址中,每个像素值的读取/存储过程的最终状态是回到IDLE 状态。

3.3 VIDEORAM 模块的结构

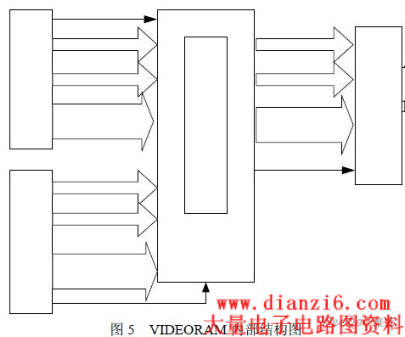

前面提到,VIEDORAM 模块是LEDINTERFACE 模块和BUFFERUPDATA 模块和共用 模块。实际上一个双端口RAM 是很容易得到的,这个模块可能使用一个静态RAM 来实现。

在FPGA 里只需综合相对简单的SRAM 的接口模块和另外两个模块,这个接口模块即 VIDEORAM 模块,事实上这不是一个真正的双端口模块。如图4 所示为VIDEORAM 内部 结构图。很容易看出,这个模块由以下几个部分组成:一个2 选1 的8 位地址选择器、一个 24 位双向三态数据总线,一个2 选1 的Wr 信号选择器。

4 FPGA 的功能实现

FPGA内部寄存器资源比较丰富,适合做同步时序电路较多的设计。FPGA是选用Xilinx 公司的有5万门的XC2S50,它有1728个逻辑单元(LC),384 个可配置逻辑快( CLB) , 32Kbit 的块RAM, 176 个可用的I/O 口。以上的几个功能模块都是在Xilinx 的ISE 平台上实现的, 三个模块共消耗62%的资源[7]。

5 结束语

本文作者的创新点:提出了一种基于FPGA 的LED 扫描屏控制系统的实现方案,通过 硬件和软件的辅助设计,完全实现了对LED 显示屏的扫描控制。基于FPGA 的硬件设计大 大降低了电路系统的复杂性,提高了整个系统的开发效率。

温馨提示; 本站的资料全部免费下载,为方便下次找到本站记得将本站加入收藏夹哦,牢记网址http://www.dianzi6.com

温馨提示; 本站的资料全部免费下载,为方便下次找到本站记得将本站加入收藏夹哦,牢记网址http://www.dianzi6.com|

此页提供基于FPGA的LED显示控制系统的设计和实现eda技术,eda技术实用教程, EDA/PLD参考。本站还有更多的EDA/PLD相关资料分享。

Copyright© www.dianzi6.com Inc. All rights reserved 。 1 2 3 4 5 6 7 8 |

|