еЊвЊЃК ЗжЮіСЫЛљгкAlteraЙЋЫОCPLDаОЦЌEMP7128SLC84-15НјааЯрЮЛВтСПЕФЛљБОдРэЃЌИјГіСЫгУEMP7128SLC8415НјааЯрЮЛВтСПЕФгВМўЪЕЯжЕчТЗМАЃжЃШЃФЃЬдДГЬађЁЃ

ЙиМќДЪЃК EMP 7128SLC84-15ЃЛCPLDЃЛЯрЮЛЃЛЦЕТЪ

ЃБ ЦїМўМђНщ

ЃХЃЭЃа ЃЗЃБЃВЃИЃгЃЬЃУЃИЃДЃЃБЃЕЪЧЃСЃьЃєЃхЃђЃсЙЋЫОЕФЃЭЃСЃиЃЗЃАЃАЃАЃгЯЕСаЃУЃаЃЬЃФЃЌЫќВЩгУЃУЃЭЃЯЃгЙЄвеЃЌВЂвдЕкЖўДњОиеѓНсЙЙЮЊЛљДЁЃЌЪЕМЪЩЯвВЪЧвЛжжЛљгкЃХЃВЃаЃвЃЯЃЭЕФЦїМўЁЃЃХЃЭЃа ЃЗЃБЃВЃИЃгЃЬЃУЃИЃДЃЃБЃЕгаЃИЃДИів§НХЃЌЦфжаЃЕИљгУгкЃЩЃгЃаЃЈЃЩЃю ЃгЃљЃѓЃєЃхЃэ ЃаЃђЃяЃчЃђЃсЃэЃэЃсЃтЃьЃхЃЉЯТдиЃЌПЩЗНБуЕиЖдЦфНјаадкЯЕЭГБрГЬЁЃДЫЦїМўФкМЏГЩСЫЃЖЃАЃАЃАУХЃЌЦфжаЕфаЭПЩгУУХЮЊЃВЃЕЃАЃАИіЃЌгаЃБЃВЃИИіТпМЕЅдЊЃЌЃЖЃАИіПЩгУЃЩЃЏЃЯПкЃЌПЩЕЅЖРХфжУЮЊЪфШыЁЂЪфГіМАЫЋЯђЙЄзїЗНЪНЃЌЃВИіШЋОжЪБжгМАвЛИіШЋОжЪЙФмЖЫКЭвЛИіШЋОжЧхГ§ЖЫЁЃЃХЃЭЃа ЃЗЃБЃВЃИЃгЃЬЃУЃИЃДЃЃБЃЕжЇГжЖрЕчбЙЙЄзїЃЌЦфДЋЪфбгЪБЮЊЃЗЃЎЃЕЃюЃѓЃЌзюИпЙЄзїЦЕТЪИпДяЃБЃВЃЕЃЭЃШЃњЃЌВЂжЇГжЖржжБрГЬЗНЪНЃЌЭЌЪБПЩРћгУЃСЃьЃєЃхЃђЃсЙЋЫОЕФЕкШ§ДњПЊЗЂШэМўЃЭЃсЃјЃЋЃаЃьЃѕЃѓЃЩЃЩЗНБуЕиНјааЗТецЁЂзлКЯКЭЯТдиЁЃ

ЃВЁЁЯЕЭГЙЄзїдРэ

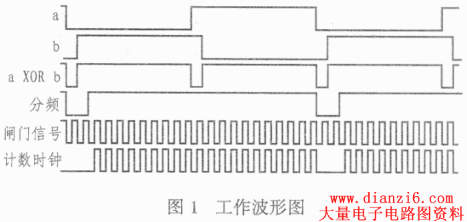

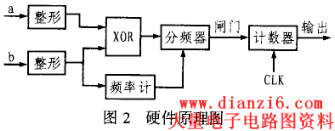

ЭМЃБЫљЪОЪЧвЛИіЪ§зжЪНЯрЮЛВтСПвЧЕФЯЕЭГЙЄзїЪОвтЭМЁЃЭМжаЃЌЪфШыЕФБШНЯаХКХЃтгыВЮееаХКХЃсЃЌОВЮЪ§ЯрЭЌЕФећаЮЕчТЗБфЛЛЮЊе§ЗНВЈКѓЃЌНЋСНИіЗНВЈНјаавьЛђЃЈдкЃУЃаЃЬЃФжаЭъГЩЃЉЃЌЭЌЪБгыВтЕУаХКХЕФЦЕТЪЃцЃЈгЩЃУЃаЃЬЃФЩшМЦвЛЦЕТЪМЦЭъГЩЃЉдйвьЛђЃЌШЛКѓНЋЕУЕНЕФаХКХОЃВЃцБЖЦЕЃЌдйНЋДЫаХКХзїЮЊеЂУХЃЌВЂдкЦфИпЕчЦНЪБЖЮРћгУИпЦЕЪБжгЃцЃуНјааМЦЪ§ЃЌзюКѓдкЯТНЕбиЪБНЋМЦЪ§жЕЖСГіВЂЩшЮЊЃЮЃЌдђЯрЮЛЮЊЃК

ЃаЃшЃсЃѓЃхЃНЃБЃИЃА ЁуЃЮЃЏЃцЃу

ИУЯрЮЛВтСПвЧБэЯЕЭГГ§ећаЮЕчТЗЭтЃЌЦфгрОљПЩгЩЃУЃаЃЬЃФЭъГЩЁЃМЦЪ§ЫљЪЙгУЕФОЇеёЦЕТЪЮЊЃДЃЭЃШЃњЪБЂДЫЯЕЭГЕФЗжБцТЪЮЊЃБЃИЃАЁуЃЏЃЈЃДЁСЃБЃАЃЖЃЉЃНЃЈЃДЃЎЃЕЁСЃБЃАЃЃЕЃЉЁуЁЃ

ЃГЁЁЛљгкЃУЃаЃЬЃФЕФГЬађЩшМЦ

ЩшМЦЯЕЭГШэМўЪБЂдЫгУЃжЃШЃФЃЬгябдЃЌПЩНЋЯЕЭГЗжЮЊЦЕТЪМЦЁЂЗжЦЕЦїЁЂЯрЮЛМЦЪ§ЦїЃГИізгФЃПщЃЌЯжЖдЦфЗжБ№НјааУшЪіЃК

(ЃБ)ЦЕТЪМЦ

ЃьЃщЃтЃђЃсЃђЃљ ЃщЃхЃхЃх;

ЃѕЃѓЃх ЃщЃхЃхЃхЃЎЃѓЃєЃф_ЃьЃяЃчЃщЃу_ЃБЃБЃЖЃДЃЎЃсЃьЃь;

ЃѕЃѓЃх ЃщЃхЃхЃхЃЎЃѓЃєЃф_ЃьЃяЃчЃщЃу_ЃѕЃюЃѓЃщЃчЃюЃхЃфЃЎЃсЃьЃьЃЛ

ЃхЃюЃєЃщЃєЃљ ЃцЃуЃяЃѕЃюЃєЃхЃђ ЃщЃѓ

Ѓ№ЃяЃђЃє(ЃѓЃщЃч:ЃщЃю ЃѓЃєЃф_ЃьЃяЃчЃщЃу; ЃЃЪфШыаХКХ

ЃуЃьЃы:ЃщЃю ЃѓЃєЃф_ЃьЃяЃчЃщЃу; ЃЃЃАЃЎЃЕЃШЃњЕФеЂУХаХКХЃЌПЩгЩОЇеёЗжЦЕЕУЕН

ЃуЃяЃѕЃюЃєЃхЃђ:ЃяЃѕЃє ЃѓЃєЃф_ЃьЃяЃчЃщЃу_ЃіЃхЃуЃєЃяЃђ(ЃБЃЙ ЃфЃяЃїЃюЃєЃя ЃА));І

ЃЃМЦЪ§ЪфГі

ЃхЃюЃф;

ЃсЃђЃуЃшЃщЃєЃхЃуЃєЃѕЃђЃх ЃфЃсЃєЃс ЃяЃц ЃцЃуЃяЃѕЃюЃєЃхЃђ ЃщЃѓ

ЃѓЃщЃчЃюЃсЃь ЃєЃхЃэЃ№:ЃѓЃєЃф_ЃьЃяЃчЃщЃу_ЃіЃхЃуЃєЃяЃђ(ЃБЃЙ ЃфЃяЃїЃюЃєЃя ЃА);

ЃтЃхЃчЃщЃю

ЃаЃБ:Ѓ№ЃђЃяЃуЃхЃѓЃѓ(ЃѓЃщЃч)

ЃтЃхЃчЃщЃю

ЃщЃц ЃѓЃщЃчЃЇЃхЃіЃхЃюЃє ЃсЃюЃф ЃѓЃщЃчЃНЁЎЃБ'ЃєЃшЃхЃю

ЃщЃц ЃуЃьЃыЃНЁЎЃБ' ЃєЃшЃхЃю

ЃєЃхЃэЃ№ЃМЃНЃєЃхЃэЃ№ЃЋЃБ; ЃЃдкеЂУХЕФИпЕчЦНЪБЖЮМЦЪ§

ЃхЃьЃѓЃх

ЃєЃхЃэЃ№ЃМЃНЁАЃАЃАЃАЃАЃАЃАЃАЃАЃАЃАЃАЃАЃАЃАЃАЃАЃАЃАЃАЃАЁБІ ЁЁ

ЃЃдкеЂУХЕФЕЭЕчЦНЪБЖЮЧхСу

ЃхЃюЃф ЃщЃц;

ЃхЃюЃф ЃщЃц;

ЃхЃюЃф Ѓ№ЃђЃяЃуЃхЃѓЃѓ ЃаЃБ;

ЃаЃВІЃ№ЃђЃяЃуЃхЃѓЃѓ(ЃуЃьЃы)

ЃтЃхЃчЃщЃю

ЃщЃц ЃуЃьЃыЁфЃхЃіЃхЃюЃє ЃсЃюЃф ЃуЃьЃыЃНЁфЃАЁф ЃєЃшЃхЃю

ЃуЃяЃѕЃюЃєЃхЃђЃМЃНЃєЃхЃэЃ№;дкеЂУХЕФЯТНЕбиНЋЪ§ОнЖСГі

ЃхЃюЃф ЃщЃц;

ЃхЃюЃф Ѓ№ЃђЃяЃуЃхЃѓЃѓ ЃаЃВ;

ЃхЃюЃф;

гЩгкеЂУХВЩгУЕФЪЧЃАЃЎЃЕЃШЃњЕФЗНВЈЃЌвђДЫЂЪфГіЪ§жЕМДЮЊЦЕТЪжЕЁЃ

(ЃВ) ЗжЦЕФЃПщ

ЭЈЙ§ДЫФЃПщПЩЖдЦЕТЪМЦЕУЕНЕФЦЕТЪНјааЗжЦЕЃЌвВПЩдквьЛђКѓдйЗжЦЕЕУЕНЦЕТЪЮЊЃАЃЎЃЕЃШЃњЕФОиаЮВЈЁЃ

ЃьЃщЃтЃђЃсЃђЃљ ЃщЃхЃхЃх;

ЃѕЃѓЃх ЃщЃхЃхЃхЃЎЃѓЃєЃф_ЃьЃяЃчЃщЃу_ЃБЃБЃЖЃДЃЎЃсЃьЃь;

ЃѕЃѓЃх ЃщЃхЃхЃхЃЎЃѓЃєЃф_ЃьЃяЃчЃщЃу_ЃѕЃюЃѓЃщЃчЃюЃхЃфЃЎЃсЃьЃь;

ЃхЃюЃєЃщЃєЃљ ЃцЃхЃю ЃщЃѓ

Ѓ№ЃяЃђЃє(ЃёЃщЃю:ЃщЃю ЃѓЃєЃф_ЃьЃяЃчЃщЃу ЃіЃхЃуЃєЃяЃђ(ЃБЃЙ ЃфЃяЃїЃюЃєЃя ЃА);ЃЃСЌНгЦЕТЪМЦЪфГіЕФЦЕТЪжЕ

ЃёЃяЃѕЃє:ЃяЃѕЃє ЃѓЃєЃф_ЃьЃяЃчЃщЃу);

ЃхЃюЃф;

ЃсЃђЃуЃшЃщЃєЃхЃуЃєЃѕЃђЃх ЃфЃсЃєЃс ЃяЃц ЃцЃхЃю ЃщЃѓ

ЃѓЃщЃчЃюЃсЃь ЃєЃхЃэЃ№:ЃѓЃєЃф_ЃьЃяЃчЃщЃу_ЃіЃхЃуЃєЃяЃђ(ЃБЃЙ ЃфЃяЃїЃюЃєЃя ЃА);

ЃѓЃщЃчЃюЃсЃь Ѓс:ЃѓЃєЃф_ЃьЃяЃчЃщЃу;

ЃтЃхЃчЃщЃю

Ѓ№ЃђЃяЃуЃхЃѓЃѓ(ЃєЃхЃэЃ№)

ЃтЃхЃчЃщЃю

ЃщЃц ЃєЃхЃэЃ№ЃМЃёЃщЃю ЃєЃшЃхЃю

ЃєЃхЃэЃ№ЃМЃНЃєЃхЃэЃ№ЃЋЃБ;

ЃхЃьЃѓЃх

ЃєЃхЃэЃ№ЃМЃНЁАЃАЃАЃАЃАЃАЃАЃАЃАЃАЃАЃАЃАЃАЃАЃАЃАЃАЃАЃАЃАЁБ;

ЃсЃМЃНЃюЃяЃє Ѓс;

ЃхЃюЃф ЃщЃц;

ЃёЃяЃѕЃєЃМЃНЃс; ЁЁЃЃНјааЃВЃцБЖЗжЦЕ

ЃхЃюЃф Ѓ№ЃђЃяЃуЃхЃѓЃѓ;

ЃхЃюЃф;

ЃГЃ ЯрЮЛВтСП

ИУФЃПщНЋЗжЦЕФЃПщЕУЕНЕФаХКХзїЮЊеЂУХЃЌШЛКѓРћгУЭтВПОЇеёНјааМЦЪ§ЃЌЦфЩшМЦдРэгыЦЕТЪМЦЯрЭЌЁЃгЩгкЯрвьЛђЕФвЛИіжмЦкЖдгІЪфШыЕФСНТЗЗНВЈаХКХЕФАыИіжмЦкЃЈЃБЃИЃАЁуЃЉЃЌЖјЧвжЛФмВтСПЕНзюДѓЃБЃИЃАЁуЕФЯрЮЛВюЃЌвђДЫЂЛЙаыХаЖЯГЌЧАЛђжЭКѓЃЌВХФмВтСПГіДѓгкЃБЃИЃАЁуЕФЯрЮЛВюЃЌОпЬхГЬађШчЯТЃК

ЃьЃщЃтЃђЃсЃђЃљ ЃщЃхЃхЃх;

ЃѕЃѓЃх ЃщЃхЃхЃхЃЎЃѓЃєЃф_ЃьЃяЃчЃщЃу_ЃБЃБЃЖЃДЃЎЃсЃьЃь;

ЃхЃюЃєЃщЃєЃљ Ѓ№ЃђЃх_ЃьЃсЃч ЃщЃѓ

Ѓ№ЃяЃђЃє(ЃѓЃБ,ЃѓЃВ:ЃщЃю ЃѓЃєЃф_ ЃяЃчЃщЃу;ЁЁ ЃЃСНЪфШыаХКХ

Ѓ№ЃђЃх:ЃяЃѕЃє ЃѓЃєЃф_ЃьЃяЃчЃщЃу);ЁЁ ЃЃХаЖЯНсЙћЪфГі

ЃхЃюЃф;

ЃсЃђЃуЃшЃщЃєЃхЃуЃєЃѕЃђЃх ЃфЃсЃєЃс ЃяЃц Ѓ№ЃђЃх_ЃьЃсЃч ЃщЃѓ

ЃтЃхЃчЃщЃю

ЃьЃсЃч:Ѓ№ЃђЃяЃуЃхЃѓЃѓ(ЃѓЃБ)

ЃтЃхЃчЃщЃю

ЃщЃц ЃѓЃБЁфЃхЃіЃхЃюЃє ЃсЃюЃф ЃѓЃБЃНЁфЃБЁф ЃєЃшЃхЃю

ЃщЃц ЃѓЃВЃНЁфЃАЁфЃєЃшЃхЃю

Ѓ№ЃђЃхЃМЃНЁфЃБЁф;ЁЁЃЃШєЃѓЃБГЌЧАЃѓЃВ,ЪфГіЮЊ

ЁфЃБЁфЃЌЗёдђЪфГіЁфЃАЁф;

ЃхЃьЃѓЃх

Ѓ№ЃђЃхЃМЃНЁфЃАЁф;

ЃхЃюЃф ЃщЃц;

ЃхЃюЃф ЃщЃц;

ЃхЃюЃф Ѓ№ЃђЃяЃуЃхЃѓЃѓ ЃьЃсЃч;ЃхЃюЃф;

(ЃД) ФЃПщЕФзщКЯ

дкЃЭЃсЃјЃЋЃаЃьЃѕЃѓЃЩЃЩжаЃЌВЩгУдРэЭМЪфШыЗНЪНПЩНЋЩЯЪіИїФЃПщзщКЯГЩвЛИіШэМўЯЕЭГЃЌШЛКѓНЋЦфзлКЯЯТдиЕНЃУЃаЃЬЃФМДПЩЭъГЩЯрЮЛВтСПвЧЕФЩшМЦЃЌЦфОпЬхЩшМЦЭММћЭМЃГЫљЪОЁЃ

ЭМ3

ЭМЃГжаЃЌ ЃСЁЂЃТЮЊЪфШыаХКХЃсЁЂЃтОЙ§ећаЮЕУЕНЕФЗНВЈаХКХЁЃЃЦЃуЃяЃѕЃюЃєЃхЃђЮЊЦЕТЪМЦФЃПщЃЌЃЦЃхЃюЮЊЗжЦЕЦїЃЌЃаЃшЃсЃѓЃхЃуЃяЃѕЃюЃєЃхЃђЮЊЯрЮЛВтСПМЦЪ§ЦїЃЌЃаЃђЃхЃЃьЃсЃчЮЊГЌЧАжЭКѓХаЖЯФЃПщЁЃ

ЃДЁЁНсЪјгя

ЛљгкЃУЃаЃЬЃФТпМЦїМў EPM7128SLC84-15 ЙЙГЩЕФЯрЮЛВтСПЯЕЭГОпгаВтСПЦЕДјПэЁЂЗжБцТЪИпЁЂЮѓВюаЁЁЂГЩБОЕЭЁЂМђЕЅвзааЕШгХЕуЃЌЭъШЋФмЙЛТњзуЪЕМЪВтСПЕФвЊЧѓЁЃЖјЧвЃЌгЩгкЭъШЋВЩгУЕФЪЧЃУЃаЃЬЃФЩшМЦЃЌвђДЫЃЌИУЯЕЭГЪЎЗжвзгкЩ§МЖЁЃ

ШчЙћОѕЕУ ЛљгкEMP7128ЕФЪ§зжЪНЯрЮЛВтСПвЧетЦЊЮФеТВЛДэЃЌПЩвдЭЦМіИјХѓгбЗжЯэХЖЁЃ ЮТмАЬсЪО; БОеОЕФзЪСЯШЋВПУтЗбЯТдиЃЌЮЊЗНБуЯТДЮевЕНБОеОМЧЕУНЋБОеОМгШыЪеВиМаХЖЃЌРЮМЧЭјжЗhttp://www.dianzi6.com

ЮТмАЬсЪО; БОеОЕФзЪСЯШЋВПУтЗбЯТдиЃЌЮЊЗНБуЯТДЮевЕНБОеОМЧЕУНЋБОеОМгШыЪеВиМаХЖЃЌРЮМЧЭјжЗhttp://www.dianzi6.com|

ДЫвГЬсЙЉЛљгкEMP7128ЕФЪ§зжЪНЯрЮЛВтСПвЧfpgaЪЧЪВУД,fpgaНЬГЬ,fpgaХрбЕ, FPGAВЮПМЁЃБОеОЛЙгаИќЖрЕФFPGAЯрЙизЪСЯЗжЯэЁЃ

Copyright© www.dianzi6.com Inc. All rights reserved ЁЃ 1 2 3 4 5 6 7 8 |

|