| 电路设计 单片机学习 PCB设计 电子制作 电工基础 电路基础 电子电路图 电脑技术 维修教程 手机数码 家电维修 电力技术 电气技术 |

| 电子基础 arm嵌入式 集成电路 模拟电子 电源管理 显示光电 楼宇控制 安防监控 控制电路 音响功放 单元电路 电子下载 维修资料下载 |

关键词: PCI总线 仲裁机制 总线的缺省占用 仲裁信号协定 仲裁算法

随着VLSI/ULSI技术的发展,可编程逻辑器件EPLD/FPGA越来越受到人们的青睐,由于它具有集成度高、速度快、开发周期短、费用低、用户可定义功能及可重复编程和擦写等许多优点,其应用领域不断扩大。这些器件的灵活性和通用性使得它们已成为研制和开发复杂数字系统的理想选择。

在PCI总线技术规范的基础上,采用EPLD实现了高速PCI总线背板中多主控设备的总线仲裁。

1 PCI总线的仲裁机制

1 PCI总线的仲裁机制

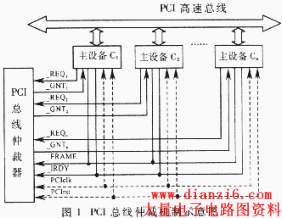

PCI总线仲裁是基于访问而不是基于时间片,也就是说,对于一个PCI总线主设备,必须为它在总线上进行的每次访问提出仲裁要求。PCI总线上采用的是并行仲裁(也叫独立请求仲裁)方案,其仲裁机制如图1所示。在这种仲裁中,每个主控器各有自己独立的总线请求线_REQ 和总线允许线_GNT 与总线仲裁器相连,相互间没有任何控制关系。仲裁器直接识别所有设备的请求,并根据一定的优先级仲裁算法选中一个设备Ci ,向它直接发出总线允许信号_GNTi。PCI总线的仲裁是“隐含的”,就是说一次仲裁可以在前一次总线访问期间完成,这样就使得仲裁的具体实现不必占用PCI总线周期。当然在总线空闲时除外。

在实际的PCI总线仲裁电路中,与仲裁直接有关的控制线除_REQ和_GNT外,还有_FRAME、_IRDY。此外,为了保证总线交换的同步,还应有一根总线时钟信号PCIclk和一根总线复位信号_PCIrst,如图1虚线所示。

2 总线的缺省占用

所谓总线的缺省占用,就是指在当前没有设备使用总线或请求总线的情况下,允许仲裁器根据一定的方式选定一个设备作为总线缺省的拥有者,并向它发出_GNT信号。选择的方式有多种,如可为某一固定设备,也可为最后一次使用总线的设备,当然也可以指定自己(仲裁器本身)为总线缺省的拥有者。

当仲裁器将某一设备确定为总线的缺省拥有者时该设备可以不通过发_REQ信号就开始一次总线操作(只要总线空闲且_GNT信号有效)。但要注意的是:如果该设备需要做多次的数据传输,它就应当发出_REQ信号,以便向仲裁器提出多次操作的请求;而如果该设备只要求做一次总线操作,它就不应当发出_REQ信号,否则仲裁器可能在它不需要使用总线的情况下又给它发出_GNT信号。

3 仲裁信号协定

综上所述, PCI总线的仲裁主要是通过_REQ和_GNT两个信号来实现的。前者用于某一设备要求占用总线的请求,后者用于允许某一设备占用总线的应答。而对于一个PCI总线主控器,必须在它真正需要总线时才能发出_REQ信号,绝不可以用_REQ信号把自己“停靠” 在总线上。只有总线仲裁器才可以指定谁是总线缺省的拥有者。

当仲裁器允许某一设备使用总线时,就向该设备发出_GNT信号;相反,当仲裁器不再允许某一设备拥有总线控制权时,可以在任意时钟撤消该设备的_GNT信号。所以,每个总线主控器在开始一次PCI总线操作时,一定要确知此时它们的_GNT信号是否有效。如果_GNT信号无效,这次操作就不可以进行。

PCI总线的仲裁信号之间必须遵循一定的协定,具体描述如下:

· 若_GNT信号撤消而_FRAME有信号,当前的总线操作是合法的,并将继续下去;

· 若总线不是处于空闲状态,有可能一个_GNT的撤消碰巧是另一个_GNT发出的同时,但如果是在空闲状态,则要求一个_GNT撤消到下一个_GNT的发出之间必须有一个时钟周期。否则可能会在AD线和PAR线上出现冲突;

· 当_FRAME无信号时,_GNT可以在任意时间撤消,以便服务于另一个主设备,或者作为对相应的_REQ撤消的响应;

· _GNT信号的每次发出,只限于相应的总线主控器可以使用总线进行一次总线操作。若该主控器还想做多次总线访问时,可以保持它的_REQ信号一直有效。此时,如果没有其它请求,或者当前的主控器具有最高优先权,仲裁器就会继续批准总线给当前主控器;

·一个主控器可以在任意时刻撤消其_REQ信号,但要注意,_REQ信号一旦撤消,仲裁器将认为该设备不再请求使用总线,因而撤消其_GNT信号。若一个主控器只希望做一次总线传输,它应当在发出_FRAME的同一时钟周期撤消_REQ;

·如果当前的主控器在它的_GNT信号发出之后(_REQ也一直有效),持续16个空闲周期还没有开始总线操作,仲裁器就可以认为当前的主控器“已坏”。因而,仲裁器可以在任意时刻撤消_GNT信号,以便服务于一个优先级更高的设备。

4 优先级仲裁算法

为了合理地控制和管理系统中需要占用总线的数据源,PCI仲裁器必须实现一个特别的优先级仲裁算法,以便在多个设备同时提出总线占用请求时,能依据该仲裁算法判决出哪个设备应获得对总线的控制权。总线仲裁可以确保任何时刻总线上最多只有一个设备发送信息,而决不会出现多个主控器同时占用总线的情况。

由于总线仲裁算法从根本上说与PCI总线技术规范无关,所以设计者可以根据实际需要自由地进行选择和修改。但要注意,设计时必须为所选用的I/O控制器及接插卡提供所要求的访问延迟保证。

总线优先级仲裁算法通常有两种,一种是固定优先级算法,一种是循环优先级算法。但不管是哪一种仲裁算法,都必须满足以下三个基本要求:

· 每一时刻只能有一个设备作为总线主控器;

· 先请求者先响应,且在一个总线操作周期之内不被打断;

· 同一时刻有几个设备发出请求时,按优先级排序响应。

所谓固定优先级算法,就是指PCI总线中各主控器的优先级是事先确定好的,在仲裁器仲裁过程中固定不变;而循环优先级算法则不同,各主控器的优先级在仲裁器的仲裁过程中不是一成不变,而是根据一定规律发生变化的。

所谓固定优先级算法,就是指PCI总线中各主控器的优先级是事先确定好的,在仲裁器仲裁过程中固定不变;而循环优先级算法则不同,各主控器的优先级在仲裁器的仲裁过程中不是一成不变,而是根据一定规律发生变化的。

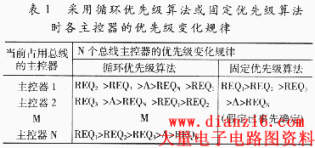

表1给出了采用循环优先级算法或固定优先级算法时,PCI总线仲裁器中N个主控器的优先级变化规律。

采用固定优先级算法,可以对那些有重要数据传输、或有大量实时数据传输以及经常需要占用总线的主设备赋予较高的优先权,以便有效地利用PCI总线周期。固定优先级算法的缺点是,它将规定每个PCI插槽的优先级,这也就规定了接插卡的插放次序,从而造成了使用上的不便。另外,固定优先级算法有时还会出现总线设备“撑死”和“饿死”的现象。相反,采用循环优先级算法则可以克服这种“饱饿”不均的弊端。在循环优先级算法中,由于其优先级随着每个总线周期动态地改变,各个设备在总线上的身份平等,获得总线占用权的机会均等。所以,在一定意义上来说,优先级循环是最公平的算法。循环优先级的缺点是当处理某些设备的大批量实时数据时会造成效率的降低。正因如此,在实际中,常常将这两种算法结合起来使用,以便构成更为灵活的仲裁机构。

5 仲裁器的EPLD编程设计

下面以支持5个总线主控器的PCI总线仲裁器为例,给出采用Altera公司的EPLD进行功能实现的主要设计思路,其中,所用编程语言为Altera公司的AHDL语言。该仲裁器采用循环优先级仲裁算法,且总线的缺省拥有者指定为最后一次使用总线的主设备。

5.1 PCI总线的状态机

5.1 PCI总线的状态机

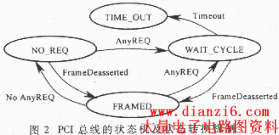

PCI总线的状态机包括三种基本状态:无任何总线请求(NO_REQ)、等待周期(WAIT_CYCLE)和帧信号_FRAME的撤消(FRAMED)。其中,_FRAME信号的撤消,意味着当前的总线操作将进入最后一个数据传输周期,此时,_IRDY有效,一旦 _TRDY也有效最后一个数据传输周期就可完成。而判断_FRAME是否撤消的具体方法就是判断_FRAME是否出现从低到高的上跳变。图2所示即为PCI总线的状态机。图中,TIME_OUT为从_GNT发出到_FRAME变为有效所允许的PCI总线周期数。

5.2 PCI总线仲裁器的状态机

由于此仲裁器最大支持5个PCI总线主控器,所以,需定义5个状态Master0、Master1、Master2、Master3、Master4用来区分当前是哪一个主控器占用总线。至于仲裁器的仲裁状态什么时候应该发生变化则由总线状态机的状态决定,具体如下:当总线状态机处于FRAMED状态,表明在最后一个数据传输周期结束后,它将释放PCI总线,此时,仲裁器便可撤消对它的_GNT信号,以便去服务于另一个主控器;当总线状态机处于NO_REQ状态,此时,需要由仲裁器来指定一个缺省的总线占用者;当总线状态机处于WAIT_CYCLE状态,且允许该设备占用总线的时间限制已到(Timeout),这时仲裁器也将撤消对它的_GNT信号,以便服务于其它的主设备。所以,若用EnChange来代表允许仲裁器仲裁状态发生变化的条件,则采用AHDL语言的具体编程如下:

EnChange=(EnCHstate ==FRAMED)#(eNchSTATE == no_req)#(TimeOut[]==TIME_OUT)

EnChange=(EnCHstate ==FRAMED)#(eNchSTATE == no_req)#(TimeOut[]==TIME_OUT)

该仲裁器中,由于采用循环优先级算法,仲裁器从每一种仲裁状态转换到其它仲裁状态的方法都是一样的,所以,下面只给出了仲裁器的仲裁状态为主控器1时向其它仲裁状态的转换机理(如图3所示)。另外,若仲裁器在刚启动时处于无效状态,则强制状态机在下一个时钟转换到Master0态。

5.3 总线允许信号_GNTi(低电平有效)的建立

在PCI对话中,由于_FRAME 和 _IRDY决定着总线的忙/闲状态。两者之中只要有一个信号成立,总线就处于忙碌状态;当两个信号都无效时,总线才处于空闲状态。所以建立_GNTi的具体编程如下:

!_GNTi=(GNTstate==Masteri)&GLOBAL(_PCIrst)&!MaskGNT;%式中,MaskGNT=_FRAME&_IRDY%

总之,本文介绍的PCI总线仲裁器,由于采用单片EPLD即可实现,所以它具有系统结构简单、成本低、可靠性高、在线修改方便及升级容易等特点。目前,采用该仲裁器的PCI高速总线背板已应用在我们研发的总线型高性能网络交换机系列中。经过近两年的实际运行表明,仲裁器工作正常,性能稳定可靠。

如果觉得 基于EPLD的PCI总线仲裁器的设计与实现这篇文章不错,可以推荐给朋友分享哦。 温馨提示; 本站的资料全部免费下载,为方便下次找到本站记得将本站加入收藏夹哦,牢记网址http://www.dianzi6.com

温馨提示; 本站的资料全部免费下载,为方便下次找到本站记得将本站加入收藏夹哦,牢记网址http://www.dianzi6.com|

此页提供基于EPLD的PCI总线仲裁器的设计与实现fpga是什么,fpga教程,fpga培训, FPGA参考。本站还有更多的FPGA相关资料分享。

Copyright© www.dianzi6.com Inc. All rights reserved 。 1 2 3 4 5 6 7 8 |

|