| 电路设计 单片机学习 PCB设计 电子制作 电工基础 电路基础 电子电路图 电脑技术 维修教程 手机数码 家电维修 电力技术 电气技术 |

| 电子基础 arm嵌入式 集成电路 模拟电子 电源管理 显示光电 楼宇控制 安防监控 控制电路 音响功放 单元电路 电子下载 维修资料下载 |

程序设计与仿真。

1. 出租车计价器--文件名:taxi.hd

--功能:出租车计价器

--最后修改日期:2004.4.9

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity taxi is

port ( clk_240 :in std_logic; --频率为240Hz的时钟

start :in std_logic; --计价使能信号

stop:in std_logic; --等待信号

fin:in std_logic; --公里脉冲信号

cha3,cha2,cha1,cha0:out std_logic_vector(3 downto 0); --费用数据

km1,km0:out std_logic_vector(3 downto 0); --公里数据

min1,min0: out std_logic_vector(3 downto 0)); --等待时间

end taxi;

architecture behav of taxi is

signal f_15,f_16,f_1:std_logic; --频率为15Hz,16Hz,1Hz的信号

signal q_15:integer range 0 to 15; --分频器

signal q_16:integer range 0 to 14; --分频器

signal q_1:integer range 0 to 239; --分频器

signal w:integer range 0 to 59; --秒计数器

signal c3,c2,c1,c0:std_logic_vector(3 downto 0); --制费用计数器

signal k1,k0:std_logic_vector(3 downto 0); --公里计数器

signal m1:std_logic_vector(2 downto 0); --分的十位计数器

signal m0:std_logic_vector(3 downto 0); --分的个位计数器

signal en1,en0,f:std_logic; --使能信号

begin

feipin:process(clk_240,start)

begin

if clk_240'event and clk_240='1' then

if start='0' then q_15<=0;q_16<=0;f_15<='0';f_16<='0';f_1<='0';f<='0';

else

if q_15=15 then q_15<=0;f_15<='1'; --此语句得到频率为15Hz的信号

else q_15<=q_15+1;f_15<='0';

end if;

if q_16=14 then q_16<=0;f_16<='1'; --此语句得到频率为16Hz的信号

else q_16<=q_16+1;f_16<='0';

end if;

if q_1=239 then q_1<=0;f_1<='1'; --此语句得到频率为1Hz的信号

else q_1<=q_1+1;f_1<='0';

end if;

if en1='1' then f<=f_15; --此语句得到计费脉冲f

elsif en0='1' then f<=f_16;

else f<='0';

end if;

end if;

end if;

end process;

process(f_1)

begin

if f_1'event and f_1='1' then

if start='0' then

w<=0;en1<='0';en0<='0';m1<="000";m0<="0000";k1<="0000";k0<="0000";

elsif stop='1' then

if w=59 then w<=0; --此语句完成等待计时

if m0="1001" then m0<="0000"; --此语句完成分计数

if m1<="101" then m1<="000";

else m1<=m1+1;

end if;

else m0<=m0+1;

end if;

if m1&m0>"0000001"then en1<='1'; --此语句得到en1使能信号

else en1<='0';

end if;

else w<=w+1;en1<='0';

end if;

elsif fin='1' then

if k0="1001" then k0<="0000"; --此语句完成公里脉冲计数

if k1="1001" then k1<="0000";

else k1<=k1+1;

end if;

else k0<=k0+1;

end if;

if k1&k0>"00000010" then en0<='1'; --此语句得到en0使能信号

else en0<='0';

end if;

else en1<='0';en0<='0';

end if;

cha3<=c3;cha2<=c2;cha1<=c1;cha0<=c0; --费用数据输出

km1<=k1;km0<=k0;min1<='0'&m1;min0<=m0; --公里数据、分钟数据输出

end if;

end process;

process(f,start)

begin

if start='0' then c3<="0000";c2<="0001";c1<="0000";c0<="0000";

elsif f'event and f='1' then

if c0="1001" then c0<="0000"; --此语句完成对费用的计数

if c1="1001" then c1<="0000";

if c2="1001" then c2<="0000";

if c3<="1001" then c3<="0000";

else c3<=c3+1;

end if;

else c2<=c2+1;

end if;

else c1<=c1+1;

end if;

else c0<=c0+1;

end if;

end if;

end process;

end behav;

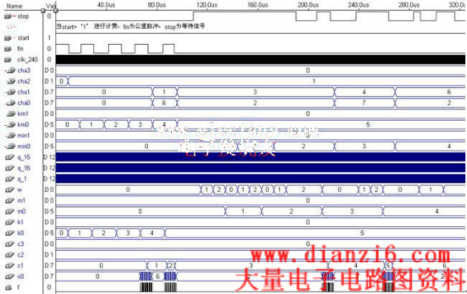

2. 程序仿真图

注:1. 仿真图中秒跟分的关系为3进制,即w为2时就归0;

2. 出租车总行驶5公里,等待累计时间为4分钟,总费用为16.2元。

图8.22.3 出租计价器程序仿真全图

温馨提示; 本站的资料全部免费下载,为方便下次找到本站记得将本站加入收藏夹哦,牢记网址http://www.dianzi6.com

温馨提示; 本站的资料全部免费下载,为方便下次找到本站记得将本站加入收藏夹哦,牢记网址http://www.dianzi6.com|

此页提供出租车计价器VHDL程序fpga是什么,fpga教程,fpga培训, FPGA参考。本站还有更多的FPGA相关资料分享。

Copyright© www.dianzi6.com Inc. All rights reserved 。 1 2 3 4 5 6 7 8 |

|