| 电路设计 单片机学习 PCB设计 电子制作 电工基础 电路基础 电子电路图 电脑技术 维修教程 手机数码 家电维修 电力技术 电气技术 |

| 电子基础 arm嵌入式 集成电路 模拟电子 电源管理 显示光电 楼宇控制 安防监控 控制电路 音响功放 单元电路 电子下载 维修资料下载 |

摘要: HDLC(高级数据链路控制)的一般实现方法为采用ASIC器件和软件编程等。应用ASIC器件时设计简单,但灵活性较差;软件编程方法灵活,但占用处理器资源多,执行速度慢,实时性不易预测。FPGA器件采用硬件处理技术,可以反复编程,能够兼顾速度和灵活性,并能多路并行处理,实时性能能够预测和仿真。在中小批量通信产品的设计中,FPGA是取代ASIC实现HDLC功能的一种合适选择。 采用Altera公司的FPGA芯片,在MAX+plus II软件平台上实现了多路HDLC电路的设计,并已在某通信产品样机中应用成功。

关键词: 数据通信; HDLC; CRC校验; FPGA; MAX+plus II

1 引言

HDLC(High-level Data Link Control Procedures, 高级数据链路控制规程)广泛应用于数据通信领域,是确保数据信息可靠互通的重要技术。实施HDLC的一般方法通常是采用ASIC(Application Specific Integrated Circuit,特定用途集成电路) 器件和软件编程等。

HDLC的ASIC芯片有Motorola公司的MC92460、ST公司的MK5025、Zarlink公司的MT8952B等。这些集成电路使用简易,功能针对性强,性能可靠,适合应用于特定用途的大批量产品中。但由于HDLC标准的文本较多,ASIC芯片出于专用性的目的难以通用于不同版本,缺乏应用灵活性。例如CCITT、ANSI、ISO/IEC等都有各种版本的HDLC标准,有的芯片公司还有自己的标准,对HDLC的CRC(Cyclical Redundancy Check,循环冗余码校验)序列生成多项式等有不同的规定。况且,专用于HDLC的ASIC芯片其片内数据存储器容量有限,通常只有不多字节的FIFO(先进先出存储器)可用。对于某些应用来说,当需要扩大数据缓存的容量时,只能对ASIC芯片再外接存储器或其它电路,ASIC的简单易用性就被抵销掉了。 HDLC的软件编程方法功能灵活,通过修改程序就可以适用于不同的HDLC应用。但程序运行占用处理器资源多,执行速度慢,对信号的时延和同步性不易预测。对于多路信号的HDLC应用,处理器的资源占用率与处理路数成正比,所以软件HDLC一般只能用于个别路数的低速信号处理。

FPGA(Field Programmable Gate Array, 现场可编程门阵列)采用硬件技术处理信号,又可以通过软件反复编程使用,能够兼顾速度和灵活性,并能并行处理多路信号,实时性能能够预测和仿真。FPGA芯片虽成本略微高于ASIC芯片,但具有货源畅通、可多次编程使用等优点。目前FPGA单片所含的逻辑门和片上存储器的容量越做越大,百万门级的可编程逻辑芯片已成为寻常产品。在中小批量通信产品的设计生产中,用FPGA实现HDLC功能是一种值得采用的方法。正是有鉴于此,Innocor、Xilinx等公司推出了能在FPGA中实现HDLC功能的IP Core(Intellectual Property Core,知识产权核),但这些IP Core需要付费购买许可(License)才能使用,且在应用中受到各种限制。

本文从HDLC的基本定义出发,通过对FPGA设计输入的模块化描述,介绍一种能够在可编程逻辑芯片中实现HDLC功能的方法。

2 HDLC的帧结构和CRC校验

HDLC规程主要由帧结构、规程要素、规程类别三个部分组成[1]。为了使FPGA的设计能够实现HDLC的基本功能并能按照各项标准的规定灵活采用不同的CRC校验算法,首先回顾一下HDLC基本的帧结构形式。

HDLC是面向比特的链路控制规程,其链路监控功能通过一定的比特组合所表示的命令和响应来实现,这些监控比特和信息比特一起以帧的形式传送。

以下是ISO/IEC 3309标准规定的HDLC的基本帧结构。

| 起始标志 | 地址数据 | 控制数据 | 信息数据 | 帧校验序列 | 结束标志 |

| 01111110 | 8bits | 8bits | 8bits | 16或32bits | 01111110 |

其它的HDLC标准也有类似的帧结构。每帧的起始和结束以"7E"(01111110)做标志,两个"7E"之间为数据段(含地址数据、控制数据、信息数据)和帧校验序列。帧校验采用CRC算法,对除了插入的"零"以外的所有数据进行校验。为了避免将数据中的"7E"误为标志,在发送端和接收端要相应地对数据流和帧校验序列进行"插零"及"删零"操作。

各种HDLC间的区别之一是帧校验序列的CRC算法不同,这种不同表现在几个方面:

a. 帧校验序列的位数不同,如16位和32位等。

b. CRC生成多项式不同,如对于16位的CRC,CCITT V.41标准的多项式是x16 + x12 + x5 + 1,ANSI CRC-16标准的多项式是x16 + x15 + x2 + 1等。

c. CRC序列的初始化条件不同,如可以初始化为全"0"、全"1"等。

d. CRC计算结果的处理方式不同,如可以直接把CRC结果发送,或对CRC结果取反后再发送等。

e. 对接收到的数据做CRC校验时,合格判据不同。因为有了上述的不同处理,自然会得到不同的结果,由此造成合格判据不同。例如有的标准以校验结果"1D0F"判为无错误[2]。而有的ASIC芯片以校验结果"F0B8"判为无错误[3]。

显然,对于这些应用,可编程逻辑芯片正可以发挥自己的特长。

3 用FPGA实现HDLC功能的原理框图

对FPGA器件进行功能设计一般采用的是"Top to Down"("从顶到底")的方法,亦即根据要求的功能先设计出顶层的原理框图,该图通常由若干个功能模块组成。再把各个模块细化为子模块,对较复杂的设计还可把各子模块分成一层层的下级子模块,各层的功能可以用硬件描述语言或电路图来实现。

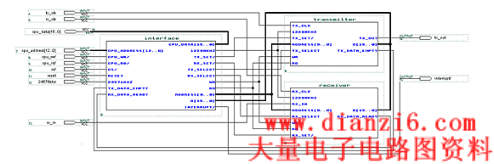

图2即为一个典型的单路双向HDLC电路的顶层电原理图设计实例。

从图中可以看出,该电路由接口模块interface、HDLC数据发送模块transmitter和HDLC

数据接收模块receiver三部分组成。当需要多路HDLC收发器时,可将若干个transmitter模块和receiver模块组合使用。以下分别对这几个模块做简要说明。

图2

3.1 接口模块interface

interface模块的主要功能是:向FPGA提供时钟;通过数据、地址总线和读写信号向FPGA读写并行数据;产生和处理中断信号。

在本例中,时钟是24.576MHz。时钟的频率越高,就可以处理更高速的数据信号,但相应的芯片功耗和价格要高一些。时钟频率还和HDLC的数据收发速率有关,一般选时钟频率正好是HDLC数据速率的整数倍,以便简化HDLC 收发器定时电路的设计。

数据总线的宽度取决于所使用的外部CPU类型。由于目前较多使用的是16位的单片处理器,因此这里采用16位的数据总线cpu_data[15..0]。当然也可以根据需要采用8位或32位的数据总线。

地址总线的宽度主要取决于HDLC所需要的数据缓存区的大小。例如,设计16路双向HDLC收发器,每个收发器要缓存256字节的数据,在使用16位数据总线时可求得地址总线的宽度至少应有12位。由于外部CPU要对FPGA实施一些控制功能,FPGA中还要考虑留出一定的地址来安排命令寄存器和状态寄存器,所以实际所需的地址总线还要再宽一些。如果HDLC的路数很多,缓存器又定得很大,FPGA内部的地址宽度会超过外部CPU可提供的地址宽度,这时可以向FPGA的特定寄存器写入数据锁存后作为内部地址来扩展地址总线。

对于外部CPU来说,FPGA可以看成是一个普通芯片,通过片选CS/、读写信号RD/和WR/,就可以选中FPGA并对其进行读写操作。

当FPGA需要向CPU传递信息时,中断信号输出端interrupt/ 变为低电平,CPU响应后可到FPGA中的状态寄存器去读取详细的中断信息并做出相应的处理。

3.2 HDLC数据发送模块transmitter

transmitter模块的主要功能是:对本路HDLC数据发送时钟tx_clk整形后产生内部发送时钟inter_tx_clk, 产生锁相于inter_tx_clk的FPGA工作时钟tx_op_clk;锁存外部CPU写入的发送数据并按指定时序启动发送;在发送数据段前加上"7E"起始标志;对发送数据逐位做CRC计算并将计算结果附在发送数据之后;对包括CRC计算值在内的数据进行"插零"操作并附上"7E"结束标志把结果输出。

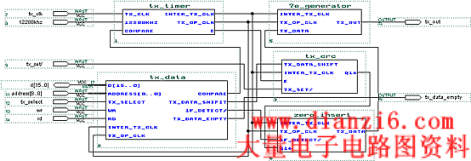

transmitter模块由发送定时子模块tx_timer、发送数据子模块tx_data、标志发生器子模块7e_generator、发送CRC计算子模块tx_crc、数据插零子模块zero_insert等组成,见图3。

HDLC的数据发送时钟tx_clk由外部电路提供(在必要时也可把这些外部电路综合进同一片FPGA),工作时钟op_clk的频率比数据发送时钟高出几倍并锁相于数据发送时钟,能以高于比特发送的速度执行对数据的操作。

图3

待发送数据是由外部CPU通过interface模块写入指定地址的缓冲存储器的。在HDLC中,可以选用的缓冲存储器类型有FIFO(先进先出)存储器、DPRAM(双端口RAM)存储器、移位寄存器等。在本设计中,发送数据的存储使用的是数据锁存移位寄存器。使用这种寄存器的优点是:写入的待发送数据经锁存后,可在任何时候(包括正在发送时)对数据的任何部分读出检查,并且数据可直接串行移位做CRC计算,简化FPGA设计。这种寄存器由数据锁存器和串行移位寄存器两部分组成,占用芯片资源较多,但对于有大量片上存储器可用的FPGA 芯片来说,这点是不成问题的。

"7E"标志加在发送数据段的前后,其时序由tx_timer确定。在发送启动时,先发"7E"再发数据。

发送CRC计算子模块tx_crc由16个带赋能端e的D触发器组成,其电路图见图4,可用来按照x16 + x12 + x5 + 1的生成多项式进行16位CRC计算。该电路的原理可参看数据通信教科书,此处不再赘述,仅说明几点:

a. 如果要改变CRC的位数,只要改变D触发器的数量。

b. 如果要改变CRC生成多项式,仅需将多项式中非零系数项对应的D触发器的输出与d1信号"异或"后送至下一个D触发器的输入。

c. 通过给D触发器的PRN端或CLRN端置"0",就可改变CRC计算的初始值。

这个例子可说明用FPGA设计的CRC电路具有极大的灵活性。

图4

发送的数据经CRC计算并将计算结果附在数据后面,再经"插零"后附上"7E"标志就可输出。"插零"操作由子模块zero_insert完成。子模块tx_data监视着每一个串行移出的数据,当发现数据流中出现五?quot;1"时,就输出控制信号1f_detect/ 暂停数据移位,此时子模块zero_insert向数据流插入一个"0"比特。

子模块tx_data中存储着待发送数据的比特长度值,并随时和已发送数据的比特长度值比较。当出现两者相等的情况时,判定为数据发送完毕,子模块tx_crc停止CRC计算并把计算结果输出。再经过16个数据时钟后,子模块7e_generator发出"7E"作为结束标志,同时向接口模块interface发出tx_data_empty信号表示数据发送结束。

3.3 HDLC数据接收模块receiver

receiver模块的主要功能是:产生与本路HDLC接收数据时钟同步的FPGA工作时钟;在接收的数据流中检测有无"7E"标志;当检测到数据流中有"1F"信号时,对数据进行"删零"操作;对经"删零"后的数据进行CRC校验;把接收到的数据进行串/并转换并存入双端口RAM;当接收到结束标志后,检查CRC校验值是否正确,向interface模块发出rx_data_ready信号。

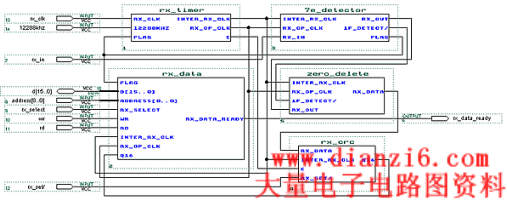

receiver模块由接收定时子模块rx_timer、接收数据子模块rx_data、标志检测子模块7e_detector、数据删零子模块zero_delete、接收CRC校验子模块 rx_crc等组成,见图5。

对比receiver模块和transmitter模块,虽然两者一些子模块的功能是相逆的,但其原理是类似的,因此不再重复说明。

在receiver模块中采用了双端口RAM来作为HDLC接收数据缓存器,因此FPGA内部向双端口RAM写入数据和FPGA外部向双端口RAM读出数据可以分别通过两个端口独立的数据地址总线同时进行。

图5

限于篇幅,以上所述仅为设计HDLC电路的大致框架,许多细节已被省略了。

4 应用实例

根据上述设计方法,已成功地在可编程逻辑芯片上实现了多路HDLC的设计。

设计输入在Altera公司的MAX+plus II[4] 10.0版本的软件平台上进行。首先考虑拟设计的电路有多少路HDLC收发器、需要多少内部存储器、工作速率多少、对外部处理器的接口有何要求等。根据这些考虑,以电路图和AHDL语言结合的方法进行设计输入。对于时序电路,主要采用电路图输入的方法;对于地址译码等功能电路,采用AHDL语言描述;对于存储器、锁存器及移位寄存器等,尽量采用MAX+plus II中LPM(参数化模块库)提供的模块来实现。全部设计输入完成后,对设计进行编译、仿真。在波形仿真器内给定输入信号,检查输出的波形是否符合设计预期。反复多次进行修改,确认无误后可将设计结果下载到FPGA芯片。

FPGA芯片选用的是Altera公司的ACEX 1K系列[5]。该系列是Altera公司面向通信和消费类数字产品推出的低功耗、高密度的高性能FPGA集成电路,具有可与ASIC相比拟的价位。ACEX 1K系列器件内部采用基于LUT的架构,最大逻辑门数为10万门;可提供的片内存储器最大为49152比特;最小时延仅数纳秒,实际电路总时延在数十纳秒左右;能够满足一般HDLC的要求。ACEX 1K系列FPGA器件工作电压为2.5伏,I/O接口电压可选为2.5伏或3.3伏,配置芯片可选Altera公司的EPC1型。

设计出的具有多路HDLC功能的FPGA芯片已应用于船舶AIS(Automatic Identification System,自动识别系统)样机的无线数据通信链路中,成功实现了双向数据通信。

5 结束语

FPGA提供了一种取代ASIC芯片的选择,以上所述仅是用FPGA实现HDLC功能的一个简单介绍。在通信产品的设计中,如果原已使用了可编程逻辑芯片来实现某些功能的话,只要改用更大容量的FPGA芯片,就可以将类似于HDLC这样的功能都集成进去。如使用Altera 公司的Quartus II软件来进行同类设计,则功能更强大,更能支持"Top to Down"的设计方法,并且支持Cyclone等大规模FPGA芯片。此外,Xilinx公司新推出90纳米工艺的Spartan-3系列低成本FPGA芯片,也可作为取代ASIC的一种选择。显然,FPGA在通信技术中的应用十分值得重视,并正受到越来越多的关注。(2003.11)

参考文献

1 张德民. 数据通信,P.194. 北京:科学技术文献出版社,1997.8

2 ISO/IEC 3309: Information technology-Telecommunications and information exchange between systems-High-level data link control (HDLC) procedures-Frame structure, P.4. Switzerland: International Electrotechnical Commission, Jun 2002

3 Zarlink Semiconductor. MT8952B HDLC Protocol Controller, P.3-64. March 1997

4 Altera Corporation. MAX+plus II, Version 10.0, Sep 2000

5 Altera Corporation. ACEX 1K Programmable Logic Family Data Sheet, Altera Digital Library,Version 3,2001

温馨提示; 本站的资料全部免费下载,为方便下次找到本站记得将本站加入收藏夹哦,牢记网址http://www.dianzi6.com

温馨提示; 本站的资料全部免费下载,为方便下次找到本站记得将本站加入收藏夹哦,牢记网址http://www.dianzi6.com|

此页提供HDLC的FPGA实现方法fpga是什么,fpga教程,fpga培训, FPGA参考。本站还有更多的FPGA相关资料分享。

Copyright© www.dianzi6.com Inc. All rights reserved 。 1 2 3 4 5 6 7 8 |

|