| 电路设计 单片机学习 PCB设计 电子制作 电工基础 电路基础 电子电路图 电脑技术 维修教程 手机数码 家电维修 电力技术 电气技术 |

| 电子基础 arm嵌入式 集成电路 模拟电子 电源管理 显示光电 楼宇控制 安防监控 控制电路 音响功放 单元电路 电子下载 维修资料下载 |

在1.3~1.55 gm波长光纤通信窗口,广泛使用的是III-V族InGaAs、InGaAsP探测器。这些III-V族探测器性能优异,工作速率可达20Gb/s乃至达到40Gb/s,有很好的响应度和量子效率。然而,由于工艺结构复杂使得这样的探测器价格昂贵限制了其广泛使用。因此人们把目光投向了廉价可批量生产的硅基探测器,然而硅的禁带宽度为1.12eV对波长大于1.1 gm的波长光不吸收。为了扩展波长响应范围,可以通过往硅中掺锗的方法减小其禁带宽度,从而使吸收波长往长波长方向移动。锗的禁带宽度为0.61 eV,在1.3~1.55 ptm波长范围内有较高的吸收系数。根据Fromherz T[72],si1-xGex体材料的带隙为

虽然可以通过调整合金中锗的含量来调整si1-xGex的禁带宽度,然而也因此会产生大的晶格失配。常温下硅和锗的晶格常数分别为0.54310 nm和0.56575 nm,晶格失配度达4.17%。对于这么大的晶格失配,会引入较高的位错密度,不但减小了载流子迁移率,还使得器件有较大暗电流。但是当SiGe合金层较薄小于临界厚度时,可通过SiGe应变层的应变来补偿晶格失配,从而得到较小位错密度的SiGe/Si。对于锗组分为0.2时,临界厚度仅为15 nm,这么窄的锗吸收层对量子效率将产生不利影响。当合金厚度超过临界厚度时表面位错密度达1012cm-2[73],严重影响器件性能。通过生长渐变缓冲层,再在缓冲层上生长SiGe可以得到位错密度为104cm-2的Si0.8Ge0.2。通过退火生长方法还可以使Si。:Go.2位错密度进一步降低到102cn-2[74]1。然而对于高组分锗,其晶格不匹配引起的位错还仍有待解决。

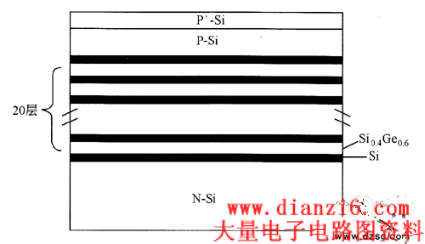

SiGe探测器不但能探测到红外波段,而且它比纯硅有更大的吸收系数,因此能制作出薄吸收层、高量子效率的高速探测器。己研制出的双异质结构的富锗SiGe合金探测器[75~徇在1.3 gm波长下响应度达到了0.89 A/W,响应时间为50 PS。H.Temkin等人[77]报道了锗组分为0.4的Si0.4Ge0.6/Si应变超晶格PIN探测器,响应波长在1.3~1.5 gm范围内,如图1所示。通过MBE外延技术生长51.4Ge0.6和51层,由于晶格不匹配会存在较大应力,因此应严格控制应变层厚度(Si0.4Ge0.6层厚度为3~6 nm,51层厚度为21~29 nm),周期数为20~30左右。总厚度为650 nm的Si0.4Ge0.6/Si应变超晶格层作为PIN的本征吸收层。在本征吸收层上再生长掺B的P-Si,接触层为高掺杂的P+。整个器件长300 pcm,宽60gm,厚100gm,击穿电压30~38 V,在-10 V偏压下漏电流随着锗含量的增大而增大(锗含量为0.4时漏电流较小只有0.4μA,组分含量大于0.6时漏电流达到了3pA)°器件内量子效率为40%,调制带宽达2 GHz。

图1 SiGe应变超晶格PIN探测器结构

利用SiGe作为应变缓冲层,将Go生长在缓冲层上的探测器结构也被提出卩剐,如图2所示。在51衬底上分别生长0.6 gm的510 456e.55层和0.4pm的510 5560.45层,接着在400C下用超高真空化学气相淀积法生长2.5gm锗层。在生长每层缓冲层后进行15min、750°C退火能进一步降低位错密度[79~80]台阶形状结构可以通过标准光刻、刻蚀、淀积金属得到,最后生长一层200 nm 5102钝化层以减小表面暗电流。对于直径为24 gm的异质结探测器,在IV、3V、10V反向偏压下暗电流分别为0.06 pA、0.27 pA、1.07 pA。随着直径的增大暗电流还将继续增大,当直径为100 ptm时在4V反向偏压下暗电流达到了10 pA,虽然暗电流密度比在硅上直接生长锗要小,但暗电流还较大不够理想。镀上抗反射膜(ARC)之后,在1.3 ptm波长下测得的响应度分别为:0.31 A/W(0 V偏压)和0.51 A/W(2V反向偏压)。网络分析仪测得的带宽为:4.0 GHz(-3V)、6.0 GHz(-5V)、7.8 GHz(-1V)和8.1 GHz(-10V)。

图2 利用SiGe作应变缓冲层的锗探测器

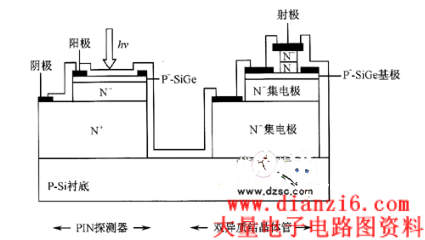

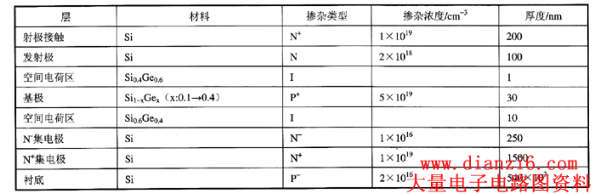

以上介绍的几种SiGe探测器都是分立的,虽然它们的制作工艺大都和微电子工艺兼容。SiGe/Si技术的发展使得异质结晶体管成为现实,这种双异质结构晶体管(HBT)可以获得很好的注入比和很高的本征频率,如果能将SiGe探测器和HBT放大电路集成在同一衬底上则可大大提高0EIC速度[81〕,如图3所示。PIN-HBT结构通过一步分子速外延而成。表1是各个层组分和掺杂特性,发射极和集电极是掺Sb的Si,基极是窄禁带宽度的SiGe,锗组分的含量从发射极这一侧的0.1渐变到集电极一侧的0.4。这样的渐变层能在基极形成“准”电场(Quasi-Electric Field)来加速电子在基区的输运过程。PIN则由N+-集电极和p+-SiGe构成,N-集电极作为PIN的本征吸收区。整个器件被台面结构隔离,PIN台面二极管面积为12 gm×13 gm。在外延生长过后,发射极接触被用电子束蒸发方法得到,接着用SF6/02干法刻蚀和KOH湿法刻蚀得到发射极台面结构。基区和集电区台面结构用干法刻蚀即可形成。最后用等离子增强化学气相淀积法淀积一层SiO,。在4 V和9 V的反向偏压下,二极管的暗电流为0.1uA和1uA°对于850 nm波长入射光和9 V反向偏压下,测得带宽为450 MHz1.1 gm厚的SiO,作为抗反射层使得在5V偏压下响应度为0.3 AIW,响应量子效率为43%。由于本征吸收层还是51层,因此p+-SiGe阳极并没有将量子效率提高太多。为了提高响应度和波长响应有必要增加本征区锗含量,然而这会增加暗电流。可以通过生长多层SiGe/Si超晶格结构在增强本征区吸收的同时,将暗电流减小到较低水平。

图3 PIN-HBT横截面结构图

表1 PIN-HBT各层组分和掺杂浓度

欢迎转载,信息来自www.dianzi6.com(www.dianzi6.com)

温馨提示; 本站的资料全部免费下载,为方便下次找到本站记得将本站加入收藏夹哦,牢记网址http://www.dianzi6.com

温馨提示; 本站的资料全部免费下载,为方便下次找到本站记得将本站加入收藏夹哦,牢记网址http://www.dianzi6.com|

此页提供在修改BiCMOS工艺条件下实现光电集成集成电路设计,半导体集成电路, 集成电路参考。本站还有更多的集成电路相关资料分享。

Copyright© www.dianzi6.com Inc. All rights reserved 。 1 2 3 4 5 6 7 8 |

|