| 电路设计 单片机学习 PCB设计 电子制作 电工基础 电路基础 电子电路图 电脑技术 维修教程 手机数码 家电维修 电力技术 电气技术 |

| 电子基础 arm嵌入式 集成电路 模拟电子 电源管理 显示光电 楼宇控制 安防监控 控制电路 音响功放 单元电路 电子下载 维修资料下载 |

三维集成电路的第一代商业应用,CMOS图像传感器和叠层存储器,将在完整的基础设施建立之前就开始。在第一部分,我们将回顾三维集成背后强大的推动因素以及支撑该技术的基础设施的现状,而在第二部分(下期),我们将探索一下三维集成电路技术的商业化。

不论是在需要考虑栅极和互连延迟的器件级别,还是在需要考虑带宽和时序问题的系统级别,都无法避免一场正在发生的完美风暴,它要求业界在如何实现微电子功能方面做出转变。影响这一转变的关键因素包括国际半导体技术蓝图(ITRS)的推迟,以及由难于集成多孔低k材料所带来的铜和低k线尺寸持续缩减的问题。与此同时,高达50%的功耗用在芯片的互连线上,即使对于65 nm工艺节点的铜互连线来说,引线电阻和寄生电容也已经成为问题。

最早认识到这些问题是在2001年,当时IEEE院士Saraswat、Rief和Meindl预测,“芯片互连恐怕会使半导体工业的历史发展减速或者止步……”,并提出应该探索电路的3D集成技术。

2007年9月,半导体工业协会(SIA)宣称:“在未来大约10-15年内,缩小晶体管尺寸的能力将受到物理极限的限制”,因此3D集成的需求变得更加明显。全新的器件结构,比如碳纳米管、自旋电子或者分子开关等,在10-15年内还不能准备好。5新型组装方法,如3D集成技术再次被提了出来。

存储器速度滞后问题是3D集成的另一个推动因素,众所周知,相对于处理器速度,存储器存取速度的发展较慢,导致处理器在等待存储器获取数据的过程中被拖延。在多核处理器中,这一问题更加严重,可能需要将存储器与处理器直接键合在一起。

3D IC集成技术的拯救

2005年2月,当《ICs Going Vertical》发表时,几乎没有读者认识到发生在3D IC集成中的技术进步,他们认为该技术只是叠层和引线键合,是一种后端封装技术。

今天,3D集成被定义为一种系统级集成结构,在这一结构中,多层平面器件被堆叠起来,并经由穿透硅通孔(TSV)在Z方向连接起来(图1)。

为制造这样的叠层结构,已经开发了很多工艺,下面所列的正是其中的关键技术:

■ TSV制作:Z轴互连是穿透衬底(硅或者其他半导体材料)而且相互电隔离的连接,TSV的尺寸取决于在单层上需要的数据获取带宽;

■层减薄技术:初步应用需减薄到大约75~50μm,而在将来需减薄到约25~1μm;

■ 对准和键合技术:或者芯片与晶圆(D2W)之间,或者晶圆与晶圆(W2W)之间。

通过插入TSV、减薄和键合,3D IC集成可以省去很大一部分封装和互连工艺。然而,目前还未完全明确,这些在整个制造工艺中需要集成在什么位置。似乎对于TSV工艺,可以在IC制造和减薄过程中,经由IDM或晶圆厂获得,而键合可以由IDM实现,也可以在封装操作中由外部的半导体组装和测试提供商(OSATS)实现,但这有可能在技术成熟时发生变化。

在将来很有可能发生的是,3D IC集成技术会从IC制造与封装之间的发展路线发生交叠时开始。

3D工艺选择

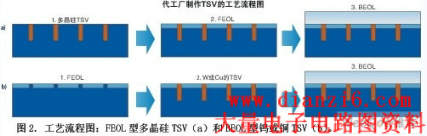

TSV可以在IC制造过程中制作(先制作通孔,via first),也可以在IC制造完成之后制作(后制作通孔,via last)。在前一种情况下,前道互连(FEOL)型TSV是在IC布线工艺开始之前制作的,而后道互连(BEOL)型TSV则是在金属布线工艺过程中在IC制造厂中实现的。

FEOL型通孔是在所有CMOS工艺开始之前在空白的硅晶圆上制造实现的(图2)。使用的导电材料必须可以承受后续工艺的热冲击(通常高于1000℃),因而只能选用多晶硅材料。在BEOL过程中制造的TSV可以使用金属钨或铜,而且在通常情况下,制作流程处于整个集成电路工艺的早期,以保证TSV不会占据宝贵的互连布线资源。在FEOL和BEOL两种情况下,TSV都必须设计进IC布线之中。

TSV也可以在CMOS器件制造完成之后制作。在键合工艺之前完成,或者在键合工艺之后完成。由于CMOS器件已经制作完成,因此在通孔形成时晶圆不需要再经受高温处理,所以可以使用铜导电材料。很明显,制作这些通孔的空白区域需要在设计芯片时就予以考虑。

如果可以选择,无论是FEOL还是BEOL方案,只要是在晶圆代工厂制作TSV,都是相对简单的选择。BEOL互连层是一个拥有不同介质和金属层的复杂混合体。刻蚀穿透这些层很困难,而且是由不同产品具体决定的。在完整的IC制造之后通过刻蚀穿透BEOL层来制作TSV会阻碍布线通道,增加布线复杂性并增加芯片尺寸,可能会需要一个额外的布线层。既然诸如TSMC(中国台湾省台北)和特许(新加坡)等晶圆厂已宣称他们有意向量产化TSV制造,那么在IC制造工艺中制作通孔将成为一个更切实可行的选择。

减薄

大多数3D IC工艺中,单个IC的厚度都远低于75 μm。

温馨提示; 本站的资料全部免费下载,为方便下次找到本站记得将本站加入收藏夹哦,牢记网址http://www.dianzi6.com

温馨提示; 本站的资料全部免费下载,为方便下次找到本站记得将本站加入收藏夹哦,牢记网址http://www.dianzi6.com|

此页提供3D集成电路将如何同时实现集成电路设计,半导体集成电路, 集成电路参考。本站还有更多的集成电路相关资料分享。

Copyright© www.dianzi6.com Inc. All rights reserved 。 1 2 3 4 5 6 7 8 |

|