| 电路设计 单片机学习 PCB设计 电子制作 电工基础 电路基础 电子电路图 电脑技术 维修教程 手机数码 家电维修 电力技术 电气技术 |

| 电子基础 arm嵌入式 集成电路 模拟电子 电源管理 显示光电 楼宇控制 安防监控 控制电路 音响功放 单元电路 电子下载 维修资料下载 |

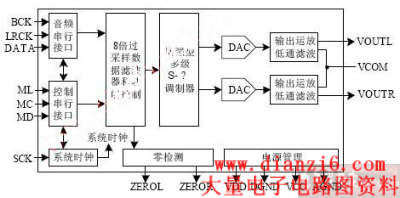

音频DAC的工作原理

高分辨率音频DAC 大都采用多级幅度量化高阶Σ - Δ调制器结构。这样,在实际应用中可以提高音频动态范围,减小对时钟抖动的敏感度,降低由此引发的失真;内置过采样的数字滤波器具有2种可供选择的滚降特性: 慢滚降和陡滚降。对于, 其内部是采用8 级幅度量化和4 级噪声整形技术。8 级调制器结构具有更高的稳定性和抗抖动能力。过采样调制器和内插滤波器的采样率是64 fs。图1 是PCM1748的结构图。

图1 的结构原理图

BCK: 音频数据位时钟;

DATA: 音频数据输入;

LRCK: 左右声道音频数据的锁存;

以上3 个引脚都是数字逻辑, 耐压能力5V。

ML: 模式控制锁存输入;

MC: 模式控制数据输入;SCK: 系统时钟输入;

ZEROL、ZEROR: 左右声道零标志位;

VDD、DGND: 数字电源;

VCC、AGND: 模拟电源;

VOUTL、VOUTR: 左右声道模拟输出;

VCOM: 公共端。

PCM1748 在正常供电电源下,是通过串行接口来送入数据和进行控制的。它的串行接口包括音频三线同步串行接口和控制三线异步串行接口。音频串行接口包括LRCK、BCK、DATA。其中,BCK是串行音频位时钟。它的功能是将DATA上现有的数据通过此时钟作用送入音频接口的移位寄存器内,并且注意串行数据是在BCK的上升沿送入音频接口的。LRCK是串行音频接口的左/右声道数据字锁存时钟。它的功能是将数据锁存到接口内部的移位寄存器中。这里应当注意,无论BCK还是LRCK都应当与系统时钟SCK同步,因而最好LRCK和BCK应从系统时钟SCK 获取。同时,LRCK与采样频率fs 一致。BCK可选择为32、48 或64 倍的采样频率。PCM1748支持工业标准的音频数据格式,包括标准格式、I2S 格式和左对齐格式。格式选择是通过控制寄存器来设置的。所有格式都需要二进制补码,高位在前的音频数据,如图2所示的左对齐格式及其操作时序。

PCM1748 具有用户可编程的模式控制。这些可编写来实现控制功能的。其中MD 是串行数据输

入,用来写模式寄存器;MC是串行位时钟,用来将数据移入控制口;ML 是控制口的锁存时钟,是将控制字锁存到寄存器中。所有的串行控制口的写操作都是采用16 位数据字,如图3 所示。其中最高位为0;IDX[6~0]是标志位,它为写操作提供寄存器索引或地址, 低7 位D[7~0]是写入到该地址的寄存器数据值。图4 表明这一写入时序。通过串行口的正确控制及特定音频数据的输入,在音频特定的采样频率及时钟控制下,再辅以必要的外围电源和输出电路,PCM1748 就可以正常地进行音频数据转换了。

温馨提示; 本站的资料全部免费下载,为方便下次找到本站记得将本站加入收藏夹哦,牢记网址http://www.dianzi6.com

温馨提示; 本站的资料全部免费下载,为方便下次找到本站记得将本站加入收藏夹哦,牢记网址http://www.dianzi6.com|

此页提供音频DAC的工作原理模拟电子技术基础,模拟电子电路, 模拟电子技术参考。本站还有更多的模拟电子技术相关资料分享。

Copyright© www.dianzi6.com Inc. All rights reserved 。 1 2 3 4 5 6 7 8 |

|