ΓΓΓΓœ÷¥ζΈΔ¥ΠάμΤςΓΔ ΐΉ÷–≈Κ≈¥ΠάμΤςΚΆΉ®”ΟΦ·≥…Βγ¬ΖΒ»ΦΦ θΒΡΖ…ΥΌΖΔ’ΙΘ§“―≥…ΈΣΒγ¥≈Η…»≈ΒΡ÷ς“Σά¥‘¥ΓΘ»γΫώ ΒΡ÷ς“ΣΖχ…δ‘¥≤Μ‘Ό «”…≤ΜΚœάμΒΡ≤ΫœΏΓΔΑεΫαΙΙΓΔΉηΩΙ ß≈δΜρΒγ‘¥≤ΜΈ»Ε®‘≠“ρΥυ≤ζ…ζΓΘΤςΦΰΒΡΙΛΉςΤΒ¬ “―¥” 20ΓΪ50 MHzΖΔ’ΙΒΫΝΥ200ΓΪ5000 MHzΘ§…θ÷ΝΗϋΗΏΓΘΥφΉ≈ ±÷”ΤΒ¬ ΒΡΧα…ΐΘ§ΟΩΗωVLSIΤςΦΰ¥φ‘Ύ«–ΜΜΒγΝςΘ§«– ΜΜΒγΝςΒΡΗΒάο“ΕΤΒΤΉ≤ζ…ζRFΡήΝΩΘ§ ΙΒΟ ΐΉ÷ΤςΦΰ±Ί»ΜΜα¥φ‘ΎΖχ…δΓΘ

ΓΓΓΓœ÷¥ζΦ·≥…Βγ¬ΖΙΛ“’ΒΡΖΔ’Ι ΙΒΟ…œΑΌΆρΒΡΨßΧεΙή±ΜΦ·≥…ΒΫ“ΜΩι–ΓΙηΤ§…œΘ§…ζ≤ζΙΛ“’¥οΒΫΝΥ0.18 ΠΧmœΏΩμ ΓΘΥδ»ΜΙηΤ§≥Ώ¥γ≤ΜΕœ ’ΥθΘ§ΒΪ‘ΣΦΰ ΐΝΩ‘ωΦ”ΝΥΘ§ ΙΒΟ≤ζΤΖΒΡ≈ζΝΩ…ζ≤ζΓΔΫΒΒΆ÷Τ‘λ≥…±Ψ≥…ΈΣΩ…ΡήΓΘΆ§ ±Θ§œΏ Ωμ‘Ϋ–ΓΘ§ΝΫΗω¬ΏΦ≠Ο≈‘ΣΦΰ÷°ΦδΒΡ¥Ϊ δ―” ±ΨΆ‘ΫΕΧΓΘΒΪ±Ώ―ΊΥΌ¬ Φ”ΩλΘ§Ζχ…δΡήΝΠ“≤ΨΆΥφ÷°‘ω«ΩΘ§Ή¥Χ§«–ΜΜ–ß ”Π‘ΎΦ·≥…–ΨΤ§ΡΎ≤Ω÷°ΦδΗ–”ΠΒΡΉς”Οœ¬Θ§Φ”¥σΝΥΡήΝΩΥπΚΡΓΘ

ΓΓΓΓΙηΤ§–η“Σ¥”Βγ‘¥Ζ÷≈δΆχ¬γ÷–ΜώΒΟΒγΝςΘ§÷Μ”–Β±ΒγΝς¥οΒΫ“ΜΕ® ΐ÷Β ±≤≈Ρή«ΐΕ·¥Ϊ δœΏΓΘ±Ώ―ΊΥΌ¬ ‘ΫΩλΘ§ΨΆ –η“ΣΧαΙ©¥οΒΫΗϋΩλΥΌ¬ ΒΡ÷±ΝςΒγΝςΓΘ«–ΜΜΩΣΙΊ‘ΎΒγ‘¥Ζ÷≈δΆχ¬γ÷–ΒΡά¥ΜΊΉΣΜΜΘ§Μα‘ΎΒγ‘¥ΑεΚΆΫ”ΒΊΑε÷°Φδ“ΐ Τπ≤νΡΘΒγΝςΒΡ≤ΜΤΫΚβΓΘΥφΉ≈Ι≤ΡΘΓΔ≤νΡΘΒγΝςΒΡ ßΒςΘ§‘ΎEMI≤β ‘÷–Θ§ΜαΖΔœ÷Ι≤ΡΘΒγΝς‘ΎΒγά¬ΉιΉΑΝ§Ϋ”¥ΠΜρ PCB‘ΣΦΰ÷–≤ζ…ζΖχ…δΓΘ

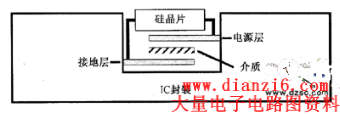

ΓΓΓΓ‘ΣΤςΦΰΙ©”Π…ΧΩ…“‘≤…”Ο≤ΜΆ§ΒΡΦΦ θΑ―»ΞώνΒγ»ί«Ε»κΒΫΦ·≥…–ΨΤ§Β±÷–ΓΘ“Μ÷÷ΖΫΖ® «Α―ΙηΨßΤ§Ζ≈ΒΫΦ·≥…–ΨΤ§ ÷°«Αœ»«Ε»κ»ΞώνΒγ»ίΘ§»γΆΦ1Υυ ΨΓΘ

ΓΓΓΓΆΦ1 Ιη–ΨΤ§ΖβΉΑΡΎ≤ΩΒΡ»ΞώνΒγ»ί

ΓΓΓΓΥΪ≤ψΫπ τΡΛ÷–Φδ‘ΌΦ”“Μ≤ψΫι÷ ≤ψΘ§ΨΆ–Έ≥…ΝΥ“ΜΗω÷ ΝΩΩ…ΩΩΒΡΤΫΑεΒγ»ίΤςΓΘ”…”ΎΆβΦ”Βγ―ΙΚήΒΆΘ§Υυ“‘Ϋι÷ ≤ψΩ…“‘ΉωΒΟΚή±ΓΓΘΕ‘”Ύ“ΜΗωΚή–ΓΒΡ«χ”ρΘ§Υϋ≤ζ…ζΒΡΒγ»ίΆξ»ΪΩ…“‘¬ζΉψ–η“ΣΘ§≤Δ«“”––ßΒΡ“ΐœΏ≥ΛΕ»«ς”ΎΝψΓΘ ΝμΆβΘ§ΤΫ––ΑεΫαΙΙΜώΒΟΒΡ–≥’ώΤΒ¬ Ζ«≥ΘΗΏΓΘ’β÷÷ΦΦ θΒΡ”≈ ΤΆΜ≥ω‘Ύ≥…±ΨΚήΒΆΘ§‘Ύ≤Μ–η“ΣΖ÷ΝΔ»ΞώνΒγ»ίΒΡ«ι Ωωœ¬Ω…“‘ΧαΗΏ–‘ΡήΓΘ

ΓΓΓΓΝμΆβ“Μ÷÷ΖΫΖ® «‘ΎΦ·≥…–ΨΤ§÷–ά¥”Ο«Ω―ΙΦΦ θ–Έ≥…»ΞώνΓΘΗΏΟήΕ»‘ΣΦΰ≥Θ≥Θ÷±Ϋ”Α―±μΟφΑ≤ΉΑΘ®SMTΘ©Βγ»ίΦ” »κΒΫΦ·≥…–ΨΤ§÷°÷–ΓΘΖ÷ΝΔΒγ»ί≥Θ‘Ύ’βΗω ±Κρ”Ο”ΎΕύ–ΨΤ§ΡΘΩι÷–ΓΘΗυΨίΙη≈Χ»κ«÷Ζε÷ΒΒγΝς≥εΦΛ«ιΩωΘ§“‘…ηΗς Υυ–ηΒΡ≥δΒγΒγΝςΈΣΜυ¥Γά¥―Γ‘ώΚœ ΒΡΒγ»ίΓΘ¥ΥΆβΘ§‘Ύ‘ΣΦΰ≤ζ…ζΉ‘ΦΛ ±ΡήΕ‘≤νΡΘΒγΝς≤ζ…ζ“÷÷ΤΉς”ΟΓΘ»γΆΦ2Υυ ΨΘ§Υδ»ΜΡΎ«Ε”–Βγ»ίΘ§‘ΎΡΘΩιΆβ≤ΩΆ§―υ–η“ΣΦ”…œΖ÷ΝΔΒγ»ίΓΘ

ΓΓΓΓ’ΐ»γ«ΑΟφΥυ ωΘ§‘ΣΦΰ‘ΎΩΣΙΊ÷ήΤΎΡΎΘ§»ΞώνΒγ»ίΧαΙ©ΝΥΥ≤ ±ΒΡ≥δΓΔΖ≈ΒγΓΘ»ΞώνΒγ»ί±Ί–κœρΤςΦΰΧαΙ©ΉψΙΜΩλ ΒΡ≥δΓΔΖ≈ΒγΙΐ≥Χ“‘¬ζΉψΩΣΙΊ≤ΌΉςΒΡ–η“ΣΓΘΒγ»ίΒΡΉ‘ΦΛΤΒ¬ »ΓΨω”ΎΚήΕύ“ρΥΊΘ§≤ΜΫωΑϋά®Βγ»ί¥σ–ΓΘ§ΜΙΑϋά®ESLΓΔESRΒ»ΓΘ

ΓΓΓΓΆΦ2 Εύ–ΨΤ§ΡΘΩιΡΎ≤ΩΒΡ»ΞώνΒγ»ί≤ΦΨ÷

ΓΓΓΓΕ‘”ΎΗΏΥΌΆ§≤Ϋ…ηΦΤΕχ―‘Θ§CMOSΙΠ¬ ΥπΚΡ±μœ÷ΈΣ»ί–‘Ζ≈Βγ–ß”ΠΓΘάΐ»γΘ§ΓΣΗω‘Ύ3.8 VΆέ―ΙΓΔ200MHzΤΒ¬ œ¬ΒΡ…η±ΗΥπΚΡ4800 mWΒΡΙΠ¬ ±Θ§ΨΆΜα¥σ‘Φ”–4000 pFΒΡ»ί–‘ΥπΚΡΓΘ’βΩ…“‘‘ΎΟΩΗω ±÷”¥ΞΖΔœ¬Ιέ≤βΒΟΒΫΓΘ

ΓΓΓΓCMOS¬ΏΦ≠Ο≈Ά®ΙΐΉ‘…μΒΡ δ»κΒγ»ίΘ§Ε‘…η±ΗΒΡώνΚœΚΆ δ»κΨßΧεΒΡ¥°ΝΣΒγ»ίά¥ΧαΙ©Ζ÷”–Βγ»ίΓΘ’β–©ΡΎ≤ΩΒγ»ί≤Δ≤ΜΒ»”Ύ‘Υ––Υυ–ηΒΡΒγ»ί÷ΒΓΘΙη≈Χ≤Μ‘ –μ Ι”ΟΝμΆβΒΡΙη≤ΡΝœ÷ΤΉς¥σμθ»ίΒΉΑεΘ§’β «“ρΈΣ÷Τ‘λΙΛ“’ΨωΕ®ΝΥ―«ΈΔΟΉ…ηΦΤΜαœϊΚΡ≤ΦœΏΩ’ΦδΘ§Ά§ ±–η“Σ÷ß≥÷―θΜ·Έο≤ψœΉΉΑ≈δΓΘ

ΜΕ”≠ΉΣ‘ΊΘ§–≈œΔά¥‘¥www.dianzi6.comΘ®www.dianzi6.comΘ©

Έ¬ήΑΧα Ψ; ±Ψ’ΨΒΡΉ Νœ»Ϊ≤ΩΟβΖ―œ¬‘ΊΘ§ΈΣΖΫ±ψœ¬¥Έ’“ΒΫ±Ψ’ΨΦ«ΒΟΫΪ±Ψ’ΨΦ”»κ ’≤ΊΦ–≈ΕΘ§άΈΦ«Άχ÷Ζhttp://www.dianzi6.com

Έ¬ήΑΧα Ψ; ±Ψ’ΨΒΡΉ Νœ»Ϊ≤ΩΟβΖ―œ¬‘ΊΘ§ΈΣΖΫ±ψœ¬¥Έ’“ΒΫ±Ψ’ΨΦ«ΒΟΫΪ±Ψ’ΨΦ”»κ ’≤ΊΦ–≈ΕΘ§άΈΦ«Άχ÷Ζhttp://www.dianzi6.com|

¥Υ“≥ΧαΙ©Φ·≥…–ΨΤ§ΡΎΒγ»ίpcb≈ύ―Β,pcb « ≤Ο¥,pcb»μΦΰ, PCB…ηΦΤ≤ΈΩΦΓΘ±Ψ’ΨΜΙ”–ΗϋΕύΒΡPCB…ηΦΤœύΙΊΉ ΝœΖ÷œμΓΘ

Copyright© www.dianzi6.com Inc. All rights reserved ΓΘ 1 2 3 4 5 6 7 8 |

|