| 电路设计 单片机学习 PCB设计 电子制作 电工基础 电路基础 电子电路图 电脑技术 维修教程 手机数码 家电维修 电力技术 电气技术 |

| 电子基础 arm嵌入式 集成电路 模拟电子 电源管理 显示光电 楼宇控制 安防监控 控制电路 音响功放 单元电路 电子下载 维修资料下载 |

随着集成电路芯片技术的飞速发展、电子产品设计业也越来越开放,很多硬件解决方案已经成为公开的资料,产品设计者的核心技术往往集中在嵌入式软件内。然而,在行业竞争日益激烈的今天,很多公司发现自己的产品投放市场后不久就被盗版,对公司造成巨大的损失,因此如何保护自己的产品已经成为嵌入式产品领域一个迫切需要解决的问题。

本文主要介绍了目前一些嵌入式系统中IP保护的方法,从安全性的角度进行了分析,并为产品开发者介绍基于ADI公司Blackfin处理器Lockbox的IP保护安全技术。

一、目前IP保护的方法

嵌入式系统的IP保护方法有很多,这些方法通常是从系统级别,硬件设计级别,芯片级别来防止反向工程或者是盗取IP。

1.系统级别的IP保护

系统级别IP保护的一个典型案例是在产品设计上嵌入硬件安全芯片,应用软件和该芯片通过密钥认证的方式来控制程序的流程,从而实现软件保护,防止软件被抄袭、篡改。并且利用安全芯片片内的自带的EEPROM,实现用户关键数据的安全存放。

这种通过增加额外芯片的方法具有较高的安全性和实用性,但是增加了一块芯片,产品的成本增加了,并且系统不能关闭JTAG,Hacker可以通过JTAG进行有效地跟踪,通过花费一定的时间和精力,可以了解并篡改系统的运行流程,因此在安全性上也存在一定的缺陷。

2.硬件设计级别的IP保护

硬件设计级别的IP保护主要是采取一些措施,比如设计硬件平台的布线,选取芯片的封装格式,来防止外部通过仪器测量存储设备的数据线或者处理器的管脚来获取信息。

首先当关键信息在外部的存储器设备和处理器之间以明文的形式通过数据线进行传输,这些数据线可以被仪器探测并中途截取,而通过采取一些布线技巧则可以避免,比如,采用多层制板,把电源层和接地层作为外层来屏蔽掉中间的铜层,并把关键的信号线,比如flash的数据线,JTAG的信号线放在中间层,以避免关键的信息被仪器探测并读取。

其次选取小管脚间距的BGA封装的芯片,把关键的信号管脚设计在最里侧,这样的芯片能进一步防止企图通过探测处理器和FLASH,DRAM这样的存储芯片之间的信号线来获取数据信息。并且通过在处理器以及存储芯片之间硬件布线时,尽可能的放得互相接近的位置,可以进一步增加探测攻击关键信号的难度。

通过设计硬件平台的布线,选取芯片的封装形式这些措施能够有效地防止探测攻击,但是BGA芯片封装的选取,多层制板以及布线技巧都会增加硬件平台的成本。

3.芯片级别的IP保护

大多数的处理器都包含有片内的存储器,比如SRAM,ROM或者是FLASH,这些存储器很难从芯片外面被读取,因此可以在这些片内的存储器存放一些关键代码和数据,这些片内数据和代码,通过一定的技术,可以限制被外部主机设备,仿真器或者其他测试设备通过JTAG测试端口来读取。

更进一步的,可以通过片内熔丝,断掉芯片JTAG管脚的外接来彻底的关掉JTAG功能,但是这样将无法进行系统出错分析以及调试。

同样,通过片内熔丝的方法,可以让芯片从片内的FLASH或者ROM启动。这些可以把一些带解密功能的Bootload放在片内FLASH中,而在片外SDRAM中放置以密文形式存放的代码。

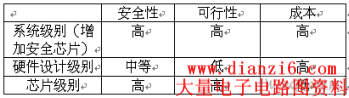

我们从安全性,可行性,以及成本三个方面对上述的三种级别的IP保护技术进行了比较,如表1-1所示。我们可以看到芯片级别的IP技术保护具有较高的安全性、可行性,以及较低的成本,是一种好的IP保护方式,我们接着要介绍的AnalogDevice公司的Blackfin处理器提供的Lockbox就是基于芯片级别的安全技术。

温馨提示; 本站的资料全部免费下载,为方便下次找到本站记得将本站加入收藏夹哦,牢记网址http://www.dianzi6.com

温馨提示; 本站的资料全部免费下载,为方便下次找到本站记得将本站加入收藏夹哦,牢记网址http://www.dianzi6.com|

此页提供基于Blackfin Lockbox的IP保护技术电子电路基础,模拟电路基础, 电路基础参考。本站还有更多的电路基础相关资料分享。

Copyright© www.dianzi6.com Inc. All rights reserved 。 1 2 3 4 5 6 7 8 |

|