| 电路设计 单片机学习 PCB设计 电子制作 电工基础 电路基础 电子电路图 电脑技术 维修教程 手机数码 家电维修 电力技术 电气技术 |

| 电子基础 arm嵌入式 集成电路 模拟电子 电源管理 显示光电 楼宇控制 安防监控 控制电路 音响功放 单元电路 电子下载 维修资料下载 |

<--关键EN(结束)←-->1 引 言

随着微电子技术的发展,现场可编程门阵列(FPGA)器件得到了飞速发展。由于该器件具有工作速度快、集成度高和现场可编程的优点,因而在数字信号处理中得到了广泛应用,越来越受到硬件电路设计工程师们的青睐。直接数字频率合成(DDS)技术具有频率分辨率高、频率变换速度快、相位可连续线性变化等特点,在数字通信系统中已被广泛采用。本文基于DDS的基本原理,利用Altera公司的FPGA芯片FLEX10系列器件完成了一个DDS系统的设计。

2 DDS的原理

DDS由相位累加器、正弦查找表、D/A转换器和低通滤波器组成,其原理如图1所示。

4 DDS的FPGA实现

FLEX10K是Altera公司1995年推出的产品系列,不仅在芯片上集成了1万个门,还首次集成了嵌入式存储器块,可为用户提供多达3K×8位的片内RAM,以满足存储器密集型应用的需要。

FLEX10K系列器件具有以下特点:高密度阵列嵌入式编程逻辑器件系列;0.5μmCMOSSRAM工艺制造;在线可编程;所有I/O端口有输入输出寄存器;快速有效地实现特大规模电路,包括存储器、DSP、专用算术逻辑、微处理器和微控制器等;专用进位链路,可实现快速加法器和计数器功能;专用级联链路,有效地实现高速多输入功能;内部三态总线,支持系统集成;支持多时钟系统的低时滞要求;具有JTAG边界扫描测试内建电路;3.3V或5.0V工作模式;由Altera公司的MAXPLUSII开发系统提供软件支持。

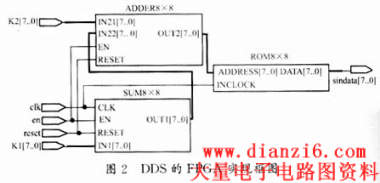

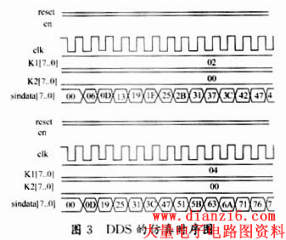

我们采用FLEX10K器件设计的DDS如图2所示。

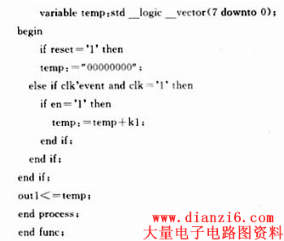

图2中,输入端K1为频率控制字,决定了DDS的频率分辨率,K2为初相控制字,clk为系统时钟,en为使能引脚,reset为复位引脚,sindata为正弦离散序列。模块SUM8×8为8位字长的相位累加器,本质上就是一个累加器,它的VHDL语言实现的主要部分如下:

模块ADDER8×8为8位加法器,决定了合成正弦波的初始相位,模块ROM8×8为被调用的LPM_ROM元件,利用它可在FLEX10K器件的内部RAM中存放一张28×8位的正弦表,当然,也可存放其它形式波形,从而实现任意波形产生。

5 结束语

本文结合DDS的基本原理,利用FPGA合成 出了正弦离散序列,配以D/A转换器和低通滤波器就可以构成一个DDS系统。

参考文献

温馨提示; 本站的资料全部免费下载,为方便下次找到本站记得将本站加入收藏夹哦,牢记网址http://www.dianzi6.com

温馨提示; 本站的资料全部免费下载,为方便下次找到本站记得将本站加入收藏夹哦,牢记网址http://www.dianzi6.com|

此页提供FPGA实现的直接数字频率合成器fpga是什么,fpga教程,fpga培训, FPGA参考。本站还有更多的FPGA相关资料分享。

Copyright© www.dianzi6.com Inc. All rights reserved 。 1 2 3 4 5 6 7 8 |

|