| 电路设计 单片机学习 PCB设计 电子制作 电工基础 电路基础 电子电路图 电脑技术 维修教程 手机数码 家电维修 电力技术 电气技术 |

| 电子基础 arm嵌入式 集成电路 模拟电子 电源管理 显示光电 楼宇控制 安防监控 控制电路 音响功放 单元电路 电子下载 维修资料下载 |

在数字电路中,把记忆输人脉冲个数的操作称为计数,计数器就是实现计数操作的时序逻辑电路。计数 器应用非常广泛,除用于计数、分频外,还用于数字测量、运算和控制,从小型数字仪表到大型数字电子 计算机,几乎无所不在,是任何现代数字系统中不可缺少的组成部分。

计数器的种类很多,按其进制不同分为二进制计数器、十进制计数器、N进制计数器;按触发器翻转是否 同步分为异步计数器和同步计数器;按计数时是增还是减分为加法计数器、减法计数器和加/减法(可逆 )计数器。下面首先介绍二进制计数器。

1.集成二进制计数器74LS161

74LS161是4位二进制同步加法计数器,除了有二进制加法计数功能外,还具有异步清零、同步并行置数 、保持等功能。74LS161的逻辑电路图和引脚排列图如图1所示,CR是异步清零端,LD是预置数控制端,D0 ,D1,D2,D3是预置数据输人端,P和T是计数使能端,C是进位输出端,它的设置为多片集成计数器的级 联提供了方便。

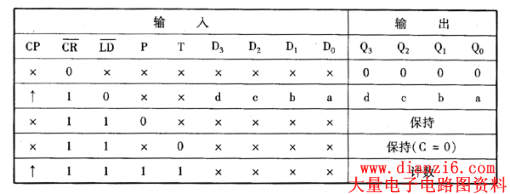

74LS161的功能表如表1所示。由表可知,74LS161具有以下功能。

图1 74LSl61的逻辑电路图和引脚图

(1)异步清零功能

当CR=0时,不管其他输人端的状态如何(包括时钟信号CP),4个触发器的输出全为零。

(2)同步并行预置数功能

在CR=1的条件下,当LD=0且有时钟脉冲CP的上升沿作用时,D3,D2,D1,D0输入端的数据将分别被Q3~Q0所接收。由于置数操作必须有CP脉冲上升沿相配合,故称为同步置数。

(3)保持功能

在CR=LD=1的条件下,当T=P=0时,不管有无CP脉冲作用,计数器都将保持原有状态不变(停止计数) 。

(4)同步二进制计数功能

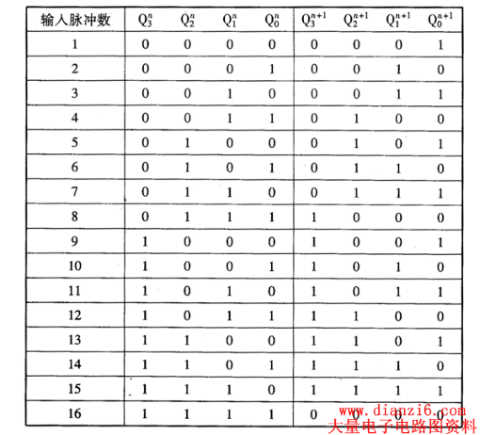

当CR=LD=P=T=1时,74LS161处于计数状态,电路从0000状态开始,连续输入16个计数脉冲后,电路 将从1111状态返回到0000状态,状态表见表2。

(5)进位输出C

当计数控制端T=1,且触发器全为1时,进位输出为1,否则为零。

表1 74LS161的功能表

表2 进制同步加法计数器的状态表

若输入计数器的CP脉冲频率为f,则从Qo端输出脉冲频率为f/2,通常也称Qo端输出信号是输人计数脉冲 CP的2分频信号,Q1端输出信号是输人计数脉冲CP的4分频信号,Q4端输出信号是输人计数脉冲CP的16分频 信号。N进制计数器可实现n分频。

2.十进制计薮器

二进制计数器电路简单,运算也方便,但人们最习惯的是十进制,所以在应用中常使用十进制计数器。使用较多的十进制计数器是按照8421BCD码进行计数的电路,计数器由“0000”状态开始计 数,每10个脉冲一个循环,也就是第10个脉冲到来时,由“1001”变为“0000”,就实现了“逢十进一” ,同时产生一个进位信号。74LS160是集成同步十进制计数器,它是按8421BCD码进行加法计数的, 74LS160的引脚图、逻辑功能与74LS161相同,只是计数状态是按照十进制加法规律来计数的,因此不再重 述。

3.利用集成计数器构成Ⅳ进制计数器

目前集成计数器的品种很多,功能完善,通用性强,在实际应用中,如果要设计各种进制的计数器,可 以直接选用集成计数器,外加适当的电路连接而成。在使用集成计数器时,不必去剖析集成电路的内部结 构,一般只需查阅手册给出的功能表和芯片引脚,按其指定的功能使用即可。

(1)集成计数器计数长度的扩展

由于4位或8位的二进制或十进制集成计数器比较常见,但其计数范围有限,当计数值超过计数范围时, 可采用计数器的级联来实现。

如用现有的″进制集成计数器构成Ⅳ进制计数器时,如果M>N,则只需一片M进制计数器;如果M<N,则 要用多片M进制计数器。集成计数器一般都设置有级联的输入/输出端,只要把它们连接起来,便可得到容 量更大的计数器。

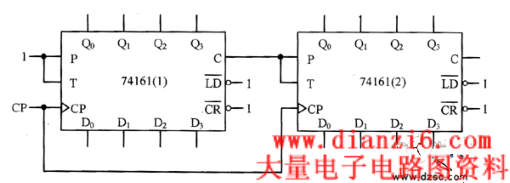

如用74LS161组成256进制计数器,因为N(=256)>M(=16),且256=16×16,所以要用两片74LS161 构成此计数器。每片均接成十六进制。

如图2所示是把两片74LS161级联起来构成的256进制同步加法计数器。两片74LS161的CP端均与计数脉冲 CP连接,因而是同步计数器。低位片(片1)的使能端P=T=1,因而它总是处于计数状态;高位片(片2 )的使能端接至低位片的进位信号输出端C,只有当片1计数至1111状态,使其C=1时,片2才能处于计数 状态。在下一个计数脉冲作用后,片1由1111状态变成0000状态,片2计人一个脉冲,同时片1的进位信号C 也变成0,使片2停止计数,直到下一次片1的C再为1。同理,如果将两片74LS161换成74LS160,可构成100 进制的同步加法计数器。

图2 集成计数器的级联

(2)用反馈清零法获得任意进制计数器

由于集成计数器一般都设置有清零端和置数端,而且无论是清零还是置数都有同步和异步之分。例如,4 位二进制同步加法计数器74LS163的清零和置数均采用同步方式,而有的只有异步清零功能。获得任意进 制计数器的方法很多,本书只介绍用反馈清零法获得任意进制计数器。

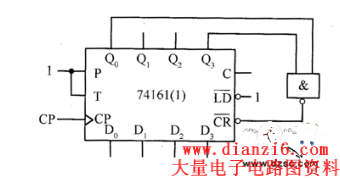

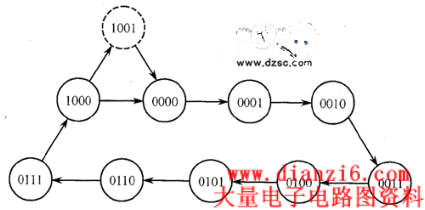

如用74LS16l构成九进制加法计数器,九进制计数器(N=9)有9个状态,而74LS161在计数过程中有16个状态(M=[6),正常循环从0000到1111,要构成九进制加法计数器,此时必须设法 跳过M-N(16 - 9=7)个状态。74LS161具有异步清零功能,在其计数过程当中,不管它的输出处于哪 一状态,只要在异步清零输人端加一低电平电压,使CR=0,74LS161的输出会立即从那个状态回到0000状 态。清零信号(CR=0)消失后,74LS161又从0000状态开始重新计数。

如图3(a)所示的九进制计数器,就是借助74LS161的异步清零功能实现的。如图3(b)所示电路是九进 制计数器的主循环状态图。

(a)用反馈清零法将74LS161接成九进制计数器 (b)用反馈清零法获得九进制计数器状态图

图3 九进制计数器

由图可知,74LSl61从0000状态开始计数,当输人第9个CP脉冲(上升沿)时,输出Q3Q2Q1Q0=1001,此 时CR=Q3Q0=0,反馈给CR端一个清零信号,立即使Q3Q2Q1Q0返回0000状态,接着CR端的清零信号也随之消 失,74LS161重新从0000状态开始新的计数周期。需要说明的是,此电路一进人1001状态后,立即叉被置 成0000状态,即1001状态仅在极短的瞬间出现,因此,在主循环状态图中用虚线表示。这样就跳过了1001 ~1111共7个状态,获得了九进制计数器。同理,如果将74LS16l换成74LS160,也可构成九进制加法计数 器。

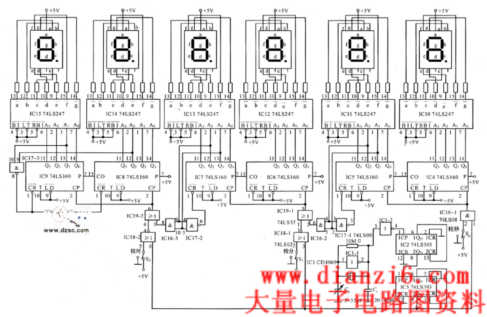

4,数字钟

数字钟由石英晶体振荡器、分频器、计数器、译码器、显示器和校时电路组成,石英晶体振荡器产生的 信号经过分频器变为秒脉冲,秒脉冲送人计数器计数,计数结果通过“时”、“分”、“秒”译码器显示 时间,电路如图4所示。

①振荡器:由CC4069非门IC1-1,IC1-2,f0=32768Hz的石英晶体振荡器、电阻和电容组成。由ICl-2 的4脚输出的频率为32768Hz的方波。

②分频器:由两个74LS393 IC2,IC3组成,74LS393是双4位二进制计数器,32768Hz的方波与IC2的I脚相 连,输人时钟脉冲,两个74LS393组成分频器,32768=215,因此,由9脚输出秒脉冲。

③计数器:由6个74LS160 IC4,IC5,IC6,IC7,IC8,IC9和相应的门电路四2输人与门74LS08、四2输人 与非门74LS00等,分别组成60进制“秒”计数器电路、60进制“分”计数器电路和24进制“时”计数器电 路。

④译码和显示电路:由6个74LS247 IC10,IC11,IC12,IC13,IC14,IC15,IC16和6个数码管组成。

⑤时间校准电路:其作用是当计时器刚接通电源或走时出现误差时,实现对“时”、“分”、“秒”的 校准,由四2输人与门74LS08、四2输入或门74LS32、四2输人或非门74LS02等组成。

图4 数字钟电路

欢迎转载,信息来源www.dianzi6.com(www.dianzi6.com)

温馨提示; 本站的资料全部免费下载,为方便下次找到本站记得将本站加入收藏夹哦,牢记网址http://www.dianzi6.com

温馨提示; 本站的资料全部免费下载,为方便下次找到本站记得将本站加入收藏夹哦,牢记网址http://www.dianzi6.com|

此页提供中规模时逻辑集成计数器集成电路设计,半导体集成电路, 集成电路参考。本站还有更多的集成电路相关资料分享。

Copyright© www.dianzi6.com Inc. All rights reserved 。 1 2 3 4 5 6 7 8 |

|