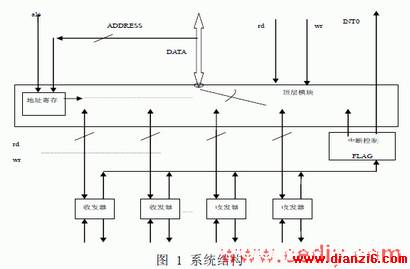

����ģ�飺����²����ģ���ź����ӣ����ݲ�ͬ�ĵ�ַ���������ݺͱ�־���ͣ��շ�����ѡ������⡣

��ϼ��Ů��˶ʿ���о�����:��Ƭ������Ϣ����. �Ŷ�Ӣ���У�˶ʿ�������ڣ��о����� :�źź���Ϣ����

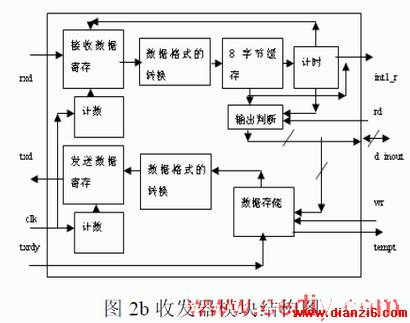

�жϹ���ģ�飺���沢���������շ���ģ��ı�־λ�����ij�շ������ж�������ʱ��Ƭ�������ж��źš��շ���ģ�飺������ݸ�ʽ��ת�������ݵĽ��պͷ��ͣ��Խ��յ������ݽ��л��棬�����Ի��� 8���ֽڵ����ݡ���ַ�Ĵ���ģ�飺�ڵ�ַ��������λ�½���ʱ����ַ������������ģ���ѷŵ�����ģ����[2]��

2.2 оƬ�뵥Ƭ������

оƬ��Ƶ�Ŀ����Ϊ��չ��Ƭ�����ڣ���������뵥Ƭ�����Ϲ����Ե�������Ҫ��ͼ 2a�����ӵ�ʾ��ͼ���ұ�Ϊ����Ƶ�оƬ��ֻ�����˸���Ƭ�����������ż�һ���շ���ģ�������������ţ���

4.4���Խ��������

�����Ѿ��Ը�ģ��ĸ��ֹ��ܽ����˺ܶ���ԣ�Ϊ�˸��õ���֤����Ƶ�оƬ��ʵ����ʹ�õĿɿ��ԣ������б�Ҫ����һ������IJ��ԣ����η�����Թ�������Ƭ�� 5�ζ���־��4����ȡ���ݣ�1

�η������ݡ����Խ������������ͼ 5g��ʾ��

���Խ�����ǻ����Կ�����1��оƬ���շ���ģ�����ͬʱ���� 2����������տ���ͬʱ���� 3�����ջ��������������ڽ������ݲ��� 8�ֽڳ�ʱ��ʱ���Զ�ֹͣ���棬Ȼ����оƬ�жϹ���ģ������ж����� 4���ж��ź��ܹ�������� 5�����շ������ж���������© 6���շ���ģ������ݱ���ȡ���֮���жϱ�־�Զ������оƬ���ٷ����ж������źš�

5 �� ��

���������һ��ʵ�ָ�Ч�മ�ڵ�һ�ж�Դ��оƬ������ƵĹ����ص㣺���жϹ������棬���õ�һ���ж�Դ�����������չ���ڣ�����֤��������жϵ���©�������������ݴ��ͷ��棬ʵ�ִ������ݵĽ��պͷ��ͣ����Ұ������ݴ����Ƿ�����żУ��λ��Ϊ���ֹ���ģʽ���ڽ���ʱ�������ݻ���Ĺ��ܡ�����������������ģ���ڵ�һ�Ŀɱ��������оƬ����ʵ�֡�

��������������ƾ����� VHDL���ʵ�֣���������·�ֹ���Ƶķ������������бȽϴ�ķ�չ�ռ䡣���зֱ����� ModelSim�� ISE�Գ�����з�����ۺϲ��ߣ��ڷ���ƽ̨����֤����ƵĿ����ԣ����нϺõ�Ӧ��ǰ����

�������ߴ��µ㣺�മ�ڵ�һ�ж�Դ��оƬ�����õ�һ���ж�Դ�����������չ���ڣ���������ģ���ڵ�һ�Ŀɱ��������оƬ����ʵ�֡�

�ο����ף�

[1]����ƽ����ڽ�.���ڵ�Ƭ���Ĵ�����չ��.�������Ϣ,2006, 03(2):13-15

[2]����գ��±� Mcs-51��Ƭ��Ӧ����ƣ�����������������ҵ��ѧ�����磬2003��65-73

[3]�����������Ʒ���ſ�ϼ������ PSoCʵ��ʱ��.�������Ϣ,2009, 11(25):136-137

[4]������������ FPGA�Ĵ���ͨ��ʵ���� CRCУ�飺˶ʿѧλ���ģ�����������������ѧ��2006

[5]�࣬���£�VHDLӲ���������������������ڶ��森�������������ӿƼ���ѧ�����磬1999��228-236

[6]�ﺽ��xilinix�ɱ���������ĸ�Ӧ������Ƽ��ɣ����������ӹ�ҵ�����磬2004��46-70

[7]���ȣ����� TL16C554ʵ�ֶ�·����ͨ�ţ����յ��Ӽ�����2005��36(3)��33-35

[8]��С����������ȣ���Ƭ���Ķമ����չ��������ƣ��������������ƣ�2004��12(11)�� 1088-1090

[9]�����̣������FPGA���������·�չ�������繤��ѧ��1996��18(4)��56-58

��ַ����ģ���� ale�źţ���Ƭ����ַ���������źţ�����ʱ����ַ�� 8λ���������������жϿ��ƺ��ϲ�ģ��ʹ��[6]��

3.5оƬ�˿�

��������ģ��ϳɺ��оƬ��ۼ���˿�������������ͼ 3��ʾ�� 1��set_mode��0,1������λ�ź��������ţ�����ģʽ��ѡ��ģʽ 1��ģʽ 2�ֱ��� 01�� 10��ѡ��2��ale����ַ���������ź��������ţ��뵥Ƭ���� ale�������� ale�½��ص�ʱ��ַ�� 8λ���浽��ַ����ģ�顣3��clk��ʱ���ź��������ţ�ʱ�ӵ�Ƶ�ʶ�Ϊ�������ݴ���Ƶ�ʵ� 4�����紮��ͨ�ŵIJ�������

9600bps���� clk��Ƶ���� 9600��4��38400Hz��

4��cs��оƬ��Ƭѡ�ź��������ţ��͵�ƽ��Ч��

5��rd��wr����Ƭ����оƬ��д�Ŀ������ţ��͵�ƽ��Ч��

6��rxd1��rxd2��rxd3��rxd4�������������š�

7��INT0���ж��ź�������ţ��½�����Ч��

8��odd_check1_o��odd_check2_o��odd_check3_o��odd_check4_o������Ƭ������żУ���־�ź�������š�

9��rdfull�����ݻ�������־�ź�������ţ����ź��á�1���͡�0�������Ƿ����շ����Ļ�����������δ����ȡ��

10��rdrdy1��rdrdy2��rdrdy3��rdrdy4�����ŷֱ����ڱ��������շ����Ƿ���æ���Ӹ��շ�����ʼ�������ݵ����ݱ���Ƭ����ȡ�������̣�����Ӧ��rdrdy���������1����

11��txd1��txd2��txd3��txd4����������������š�

12��tdempty�����������Ϊ��1��ʱ����оƬ��û�����ڷ��ͻ����ǽ�Ҫ���͵����ݡ�

13��txrdy1,txrdy2,txrdy3,txrdy4���ֱ�Ϊ�շ��� 1��2��3�� 4�ɷ���з��Ϳ�������ˣ�����Ϊ��1����ʾ���Խ��д������ݵķ��͡�

14��d_inout(7:0)��˫���������ߡ�Ӧ�뵥Ƭ�� p0��������

15��addr_h(7:0)����ַ�� 8λ��

4������ۺϼ�����

4.1 ����ۺϼ�ʵ��

������ۺ�ʹ�õĹ����� Xilinx��˾�� XST��������Ƕ�� ISE7.2i����ġ��ۺϹ��̽���������Ƶ� HDL������Ӳ���ṹ�ҹ����ǽ�����ת��ΪӲ����·�Ĺؼ����� [7-9]��������ۺ�ʱѡ�õ�оƬ��Spartan-��Eϵ�е�xc2s100e��

�ۺϹ������������ļ��Ϳ���ʵ����ƣ�ʵ�ֵIJ����У�ת�������������ļ��ϲ�Ϊһ����������ӳ�䣨�������е������ţ��ţ����ϵ�����Ԫ���У������ֲ��ߣ���Ԫ���ŵ������У�������������������ͬʱ��ȡ��ʱ�����ݣ������ɸ��ֱ��棩��

4.2 �ۺϲ��߽��������

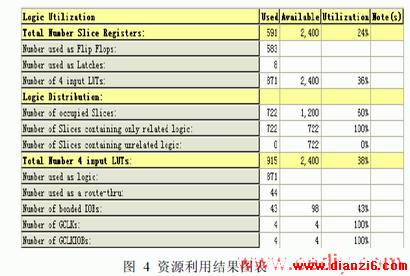

ͼ 4Ϊ��Դ���ý��ͼ������ͼ�ɼ���slices��ռ����Ϊ 722����ռ��оƬ slices������ 60����slice registers��ʹ������Ϊ 591����ռ��оƬ������ 24����4������ұ���ʹ�������� 915����ռ��оƬ���ұ������� 38����

4.3 ���ߺ����

���������ٳ��IJ��Ծ�Ϊ���ߺ�ķ�����ԣ��÷���ķ�����ʱ�ļ���������ʱ��Ϣ��ȫ����������������ʱ����������ʵ�ʲ�����ʱ�����Բ��ֲ��ߺ������ȷ���ܹ��Ϻõķ�ӳоƬ��ʵ�ʹ��������

��ܰ��ʾ; ��վ������ȫ��������أ�Ϊ�����´��ҵ���վ�ǵý���վ�����ղؼ�Ŷ���μ���ַhttp://www.dianzi6.com

��ܰ��ʾ; ��վ������ȫ��������أ�Ϊ�����´��ҵ���վ�ǵý���վ�����ղؼ�Ŷ���μ���ַhttp://www.dianzi6.com|

��ҳ�ṩ�മ�ڵ�һ�ж�Դ��оƬ��Ƶ�Ƭ������,��Ƭ��ԭ��, ά�̳�֪ʶ - ��Ƭ��ѧϰ�ο�����վ���и������Ƭ��ѧϰ������Ϸ�����

Copyright© www.dianzi6.com Inc. All rights reserved �� 1 2 3 4 5 6 7 8 |

|