жаЙњЪЧШЋЧђАыЕМЬхЪаГЁГЩГЄзюПьЕФЧјгђЃЌдЄМЦУПФъдіГЄТЪГЌЙ§25%ЃЌдвђдкгкжаЙњвбОГЩЮЊШЋЧђМЏГЩЕчТЗЯћЗбЕФжааФЁЂЕчзгВњЦЗОоДѓЕФЯћЗбЪаГЁКЭећЛњжЦдьЛљЕиЃЌЮЊСЫЬљНќжеЖЫЪаГЁКЭICгУЛЇЃЌSoCВтЪджааФКЭЪЕбщЪвдкжаЙњЕФВМОжвбОЧФШЛеЙПЊЃЌБОЮФНЋЯђФњНщЩмSoCВтЪдММЪѕСьгђУцСйЕФЬєеНКЭзюаТЕФВтЪдММЪѕЧїЪЦЁЃ

ФПЧАЃЌICЯћКФСПЕФжївЊдіГЄМЏжадкЯћЗбЕчзгЁЂЪ§ОнДІРэКЭЭЈаХШ§ДѓСьгђЃЌЦфжаЯћЗбЕчзгАќРЈЯдЪОЦїЁЂЪ§ТыЯрЛњЁЂЪ§зжЕчЪгКЭЪгЦЕгЮЯЗЛњЃЌЪ§ОнДІРэАќРЈCPUКЭДцДЂЦїЁЂЩСДцПЈЁЂЦНУцМрЪгЦїКЭвЦЖЏPCЃЌЭЈаХСьгђдђвдЪ§зжЗфЮбЕчЛАКЭЮоЯп/гаЯпЭјТчЮЊдіГЄЧ§ЖЏСІЁЃICИДдгЖШЕФШевцЬсИпЃЌЦШЪЙЩшМЦШЫдБВЩгУИќЮЊЯШНјЕФЙЄвеММЪѕЃЌНЋИќЖрЕФЙІФмМЏГЩЕНЕЅаОЦЌФкЃЌЯЕЭГМЖаОЦЌ(System on Chip, SoC)вђДЫЪмЕНЙуЗКгІгУЃЌФПБъЪЧНјвЛВННЕЕЭећЛњЯЕЭГЩшМЦЁЂВтЪдКЭжЦдьЕФГЩБОЁЃ

ФПЧАЃЌ0.25КЭ0.18umЙЄвеММЪѕеМОнжїЕМЕиЮЛЃЌ0.13umвдЯТЙЄвеММЪѕвбОдквЛаЉИпЖЫВњЦЗжаЕУЕНгІгУЃЌВЂГЪЯжМБЫйдіГЄЕФЧїЪЦЁЃВЩгУЯШНјЩшМЦЙЄвеЕФНсЙћЃЌЪЧдьГЩЩшМЦЁЂбкФЄЗбгУдкNREжаЕФБШР§ж№ФъЩЯЩ§ЃЌвбОгЩ1995ФъЕФ13%МЄдіЮЊ2003ФъЕФ62%ЃЌЭЦГіаТаЭаОЦЌЪмЕННЕЕЭГЩБОашЧѓЕФЧПОЂЧ§ЖЏЃЌЕЋЪЧЩшМЦКЭжЦдьаТаЭаОЦЌЕФзмГЩБОШДвђаТЙЄвеММЪѕЕФгІгУЖјМБОчдіМгЁЃ

ЖјСэвЛЗНУцЃЌаТаЭЕчзгВњЦЗЕФЩњУќжмЦкдНРДдНЖЬвбОЪЧВЛељЕФЪТЪЕЃЌЫќУЧДгЧаШыЪаГЁЕНЪЕЯжАйЭђЬЈЕФСПВњЙцФЃЃЌЪБМфЭЈГЃВЛЕНвЛФъЃЌвђДЫЃЌвЕНчСїДЋетбљЕФЫЕЗЈЃК90%ЕФРћШѓЪЧВњЦЗЩЯЪаКѓЭЗСљИідТВњЩњЕФЃЌЁАTime-To-MarketЁБЪЧећИіАыЕМЬхВњвЕНіДЮгкаОЦЌИДдгЖШУцЖдЕФЕкЖўДѓЬєеНЁЃ

дкНєЦШЕФЩЯЪаЪБМфКЭаОЦЌИДдгЖШШевцЬсИпЕФЫЋжибЙЦШЯТЃЌАыЕМЬхаавЕБЛЦШЙЙНЈаТЕФЭтАќСДЬѕЃЌВЂСІЭМНсГЩИќЖрЕФММЪѕСЊУЫЃЌЙВЭЌЭЦНјММЪѕКЭЪаГЁЕФЗЂеЙЃЌЦфжавЛИіживЊЧїЪЦОЭЪЧДњЙЄГЇИќЧуЯђгкЬсЙЉвЛРПзгНтОіЗНАИЃЌАяжњМЏГЩЕчТЗЩшМЦЙЋЫОИќПьЕиЭЦГіаОЦЌЃЌЖјвЕНчеМОнСьЯШЕиЮЛЕФГЇМвИќЧуЯђгкВЩгУЯШНјЕФВтЪдММЪѕЃЌБОЮФЪдЭМЖдSoCВтЪдСьгђУцСйЕФЬєеНКЭММЪѕЗЂеЙЧїЪЦзівЛИіГѕВНЬНЬжЁЃ

ДЋЭГЕФВтЪдЗНЗЈКЭСїГЬУцСйЕФЬєеН

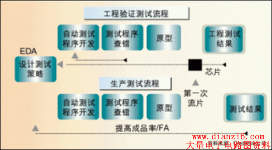

ДЋЭГЕФЩшМЦКЭВтЪдЗНЗЈНЋЩшМЦЁЂЕїЪд/бщжЄЁЂЩњВњВтЪдШ§ИіЛЗНкЙТСЂЦ№РДНјааЃЌЦфЭЛГіЕФЮЪЬтЪЧГ§ЗЧЪзПХаОЦЌжЦдьГіРДЃЌЗёдђаОЦЌВтЪдВЛПЩФмеце§ЭъГЩЃЌШчЭМ1ЫљЪОЁЃДЋЭГЕФВтЪдЗНЗЈКЭСїГЬгЩгкашвЊЖрДЮЗДИДЃЌвђЖјВЛФмЪЪгІИДдгЕФSoCДѓЙцФЃСПВњЕФашвЊЃЌИќФбНЕЕЭГЩБОЁЃЖдгкSoCВтЪдРДЫЕЃЌШЫУЧашвЊПЊЗЂИќЮЊгааЇЕФВтЪдГЬађЃЌвдТњзувЛДЮадСїЦЌЖдбщжЄЙЄОпвдМАЩњВњВтЪдЛЗНкЖдИќОпгаГЩБОаЇвцЕФВтЪдШэМўЕФашвЊЁЃ

ФПЧАЃЌШЫУЧПЊЗЂВтЪдГЬађЭЈГЃбизХЩшМЦЁЂВтЪдГЬађПЊЗЂЁЂаОЦЌдаЭбщжЄЕФЫМТЗНјааЃЌИїВПЗжЙТСЂЕиНјааШЮЮёЗжХфЁЂашЧѓЗжЮіЃЌШЛКѓЗжБ№жДааЃЌВтЪдЕФЙ§ГЬЛЙвЊВЛЖЯЭъЩЦВтЪдШэМўЁЃВтЪдГЬађПЊЗЂЭъГЩжЎКѓЃЌЛЙвЊЖдВтЪдГЬађБОЩэНјааЕїЪдЃЌЭЈГЃашвЊЖрДЮЗДИДаоИФВтЪдГЬађЃЌЪБМфЩЯвВашвЊМИИідТЕФЪБМфЁЃетЖдгкЁА6ИідТгЎЕУ90%РћШѓЁБЕФЪаГЁЗЈдђРДЫЕЪЧФбвдНгЪмЕФЃЌНтОіВтЪдГЬађБОЩэЕїЪдашвЊНЯГЄЪБМфетИіЮЪЬтЃЌЦШЪЙШЫУЧНјвЛВНИФНјЩшМЦКЭВтЪдЕФСїГЬЁЃ

вЛЬхЛЏВтЪдСїГЬ

ЮЊСЫНтОіЩЯЪіЮЪЬтЃЌЭМ2ЫљЪОЪЧвЛжжаТЕФВтЪдСїГЬЁЃЫќНЋЙЄГЬЩшМЦбщжЄВтЪдСїГЬгыЩњВњВтЪдСїГЬВЂааДІРэЁЃЦфКЫаФЫМЯыЪЧРћгУащФтдаЭЖдВтЪдЙЄГЬКЭICЩшМЦЙ§ГЬЫљашвЊЕФВтЪдГЬађ(БОЩэ)НјааВщДэКЭЕїЪдЃЌЭЌЪБЃЌвВНЋащФтдаЭгІгУЕНЩњВњВтЪдСїГЬжЎжаЃЌЭъГЩУцЯђЩњВњЕФВтЪдГЬађЕФВщДэКЭЕїЪдЁЃ

ЮЊДЫЃЌЪзЯШвЊИљОнЙЄГЬВтЪдНсЙћЃЌНјааЩшМЦжаЕФВтЪдВпТдЙцЛЎЃЌФПЕФЪЧИФНјВтЪдЗНЗЈЃЌНЕЕЭВтЪдЕФИДдгадЃЌВЂИљОнВтЪдГЩБОКЭИДдгадЖдВтЪдШЮЮёНјааЖЈвхЁЃЖјЩњВњВтЪдСїГЬжаЃЌВтЪдГЬађВщДэКЭЕїЪдЕФжївЊШЮЮёЪЧЬсИпГЩЦЗТЪЁЃ

FPGAКЭPLDдкДюНЈащФтдаЭЃЌЭъГЩЖдВтЪдГЬађЕїЪдЕФЙ§ГЬжаАчбнзХживЊзїгУЁЃЭЈЙ§РћгУащФтЛЗОГЃЌПЩвдМЋДѓЕиНЕЕЭЖдВтЪдГЬађНјааЕїЪдЫљЛЈЗбЕФЪБМфЃЌМѕЩйбкФЄДЮЪ§ЃЌНкЪЁДѓСПЁЂАКЙѓЕФбкФЄЗбгУЃЌЬсИпГЩЦЗТЪЃЌВЂдкМгПьВњЦЗЩЯЪаЪБМфЕФЭЌЪБЃЌДяЕНаОЦЌРћШѓЕФзюДѓЛЏЁЃ

ШЛЖјЃЌОЁЙмЩЯЪіЗНЗЈНтОіСЫЫѕЖЬВтЪдГЬађЕїЪдЪБМфЕФЮЪЬтЃЌЕЋЪЧЃЌашвЊдкЩшМЦКЭЩњВњСНЬѕЯпЩЯЭЌЪБЖдВтЪдГЬађНјааЕїЪдЃЌвђЖјзЪН№ЭЖШыЩЯВЂУЛгаЯджјНЕЕЭЃЌЮЊДЫЃЌCredenceЙЋЫОЬсГіСЫРћгУЙтзгНјааSoCВтЪдЕФаТММЪѕЁЃ

ЛљгкЙтзгЬНВтЕФSoCВтЪдММЪѕ

ЫцзХаОЦЌИДдгЖШЕФдіМгЃЌSoCВЩгУЕЙзАЁЂДђЯпКЭЖрВуН№ЪєЗтзАЕФЗНЪНвВдНРДдНЖрЃЌаэЖрЕиЗНВЩгУДЋЭГЕФЕчВтЪжЖЮвбОЯрЕБЗбЪБЗбСІЃЌвђДЫЃЌCredenceРћгУЙЬЬЌНўШыЭИОЕЗНЗЈЪЕЯж0.25umЕФГЩЯёЗжБцТЪЃЌРДЭъГЩЖдSoCЙиМќНкЕуЕФадФмНјааЗжЮіЁЃЭЈЙ§ВтЪдЯЕЭГХфБИЕФИпЫйВЩМЏКЭЪ§ОнДІРэФмСІЃЌАыЕМЬхжЦдьЩЬФмЙЛПьЫйНјааЩшМЦВщДэЁЂЙЪеЯЗжЮіКЭЬиеїЬсШЁЃЌДгЖјМЋДѓЕиЫѕЖЬВњЦЗЩЯЪаЪБМфВЂНЕЕЭSoCПЊЗЂЕФГЩБОЁЃ

ЛљгкЙтзгЬНВтЕФSoCВтЪдММЪѕЕФЛљБОдРэЪЧЃЌРћгУТіГхаХКХЧаЛЛВњЩњЕФФмСПЃЌМЄЗЂАыЕМЬхЕчТЗФкВПЕФЕчзгБЛМЄЗЂГіЙтзгЃЌШЛКѓЭЈЙ§ИпЫйВЩМЏКЭЪ§ОнДІРэЯЕЭГЃЌНЋВЩМЏЕФЙтзгзЊЛЏЮЊЕчзгаХКХЃЌЭЈЙ§ЖдетаЉЕчаХКХРДЗжЮіЪБађЬиеїЃЌДгЖјДяЕНЖдSoCЙиМќНкЕуНјааВтЪдЕФФПЕФЁЃЦфФПЕФЪЧМгЫйВњЦЗЕФЩЯЪаЃЌЯћГ§ВЛБивЊЕФЖрДЮЩшМЦаоИФКЭВЛБивЊЕФСїЦЌбЛЗЁЃ

SoCММЪѕЪЧ21ЪРМЭГѕвдРДбИЫйЗЂеЙЦ№РДЕФГЌДѓЙцФЃМЏГЩЕчТЗЕФжїСїММЪѕЃЌЪЧЕчзгЦїМўГжајМЏГЩЕФзюИпОГНчЁЃSoCВЩгУЯШНјЕФГЌЩюбЧЮЂУзCMOSЙЄвеММЪѕЃЌДгећИіЯЕЭГЕФНЧЖШГіЗЂЃЌНЋДІРэЛњжЦЁЂФЃаЭЫуЗЈЁЂЧЖШыЪНШэМўЕШИїВуДЮЕчТЗжБжСЦїМўЕФЩшМЦНєУмНсКЯдкЕЅИіаОЦЌЩЯЃЌЭъГЩећИіЯЕЭГЕФЙІФмЁЃ

ЫцзХSoCгІгУЕФШевцЦеМАЃЌдкВтЪдГЬађЩњГЩЁЂЙЄГЬПЊЗЂЁЂЙшЦЌВщДэЁЂСПВњЕШСьгђЖдSoCВтЪдММЪѕЬсГіСЫдНРДдНИпЕФвЊЧѓЃЌеЦЮеаТЕФВтЪдРэФюЁЂаТЕФВтЪдСїГЬЁЂЗНЗЈКЭММЪѕЃЌЪЧгІЖдЯћЗбЕчзгЁЂЭЈаХКЭМЦЫуЕШСьгђSoCгІгУЖдВтЪдММЪѕЬсГіЕФЬєеНЃЌЪЪгІВтЪдКЭзщзАЭтАќЗЂеЙЧїЪЦЕФБиШЛвЊЧѓЁЃЖдгкжаЙњМЏГЩЕчТЗВтЪдШЫдБРДЫЕЃЌСЫНтжаЙњФПЧАSoCВтЪдММЪѕЗЂеЙУцСйЕФЬєеНКЭЗЂеЙЗНЯђЃЌеЦЮеЪаГЁЕФЖЏЬЌжСЙиживЊЃЌБэ1ЫљЪОЮЊжаЙњФПЧАвбООпБИSoCВтЪдФмСІЕФВтЪджааФКЭЪЕбщЪвЕФвЛРРБэЁЃ

ШчЙћОѕЕУ SoCВтЪдММЪѕУцСйЕФЬєеНКЭЗЂеЙЧїЪЦетЦЊЮФеТВЛДэЃЌПЩвдЭЦМіИјХѓгбЗжЯэХЖЁЃ ЮТмАЬсЪО; БОеОЕФзЪСЯШЋВПУтЗбЯТдиЃЌЮЊЗНБуЯТДЮевЕНБОеОМЧЕУНЋБОеОМгШыЪеВиМаХЖЃЌРЮМЧЭјжЗhttp://www.dianzi6.com

ЮТмАЬсЪО; БОеОЕФзЪСЯШЋВПУтЗбЯТдиЃЌЮЊЗНБуЯТДЮевЕНБОеОМЧЕУНЋБОеОМгШыЪеВиМаХЖЃЌРЮМЧЭјжЗhttp://www.dianzi6.com|

ДЫвГЬсЙЉSoCВтЪдММЪѕУцСйЕФЬєеНКЭЗЂеЙЧїЪЦfpgaЪЧЪВУД,fpgaНЬГЬ,fpgaХрбЕ, FPGAВЮПМЁЃБОеОЛЙгаИќЖрЕФFPGAЯрЙизЪСЯЗжЯэЁЃ

Copyright© www.dianzi6.com Inc. All rights reserved ЁЃ 1 2 3 4 5 6 7 8 |

|