| 电路设计 单片机学习 PCB设计 电子制作 电工基础 电路基础 电子电路图 电脑技术 维修教程 手机数码 家电维修 电力技术 电气技术 |

| 电子基础 arm嵌入式 集成电路 模拟电子 电源管理 显示光电 楼宇控制 安防监控 控制电路 音响功放 单元电路 电子下载 维修资料下载 |

单片机间传统的数据通信是通过串行口进行的。在要求实时速度很快的场合时,由于串行通信的速度较慢,会产生控制算法等待数据的状态,从而延误指令输出。另外,控制算法和串行通信两个部分都要保证实时性和连续性,但是单片机最主要的任务是完成控制算法并处理控制指令输入和输出的中断。这样,单片机就有可能无法及时响应和处理串行通信的中断,从而造成数据的丢失。同时,又因为单片机中的串行寄存器SBUF只能保留一个字节的数据,就可能造成传输数据的丢失或错误,从而影响串行通信数据接收的可靠性。再者,Rs-232信号数据是ASCⅡ码,并不能被单片机直接运用,转换过程要大量占用单片机内部数据区,引起单片机资源紧张。

双端口RAM器件在单片机系统中的应用双端口RAM是一种特殊的数据存储芯片,利用双端口RAM可以实现两个单片机的总线方式的数据共享。我们以CYPRESS公司的cY7c136为例来说明其应用。图1为多单片机共享RAM方案的示意图。

1.数据线通信(从)单片机和主单片机之间的数据总线通过双端口RAM的两套数据总线端口连接起来,实现总线方式的数据共享。

2.地址线通信单片机和主单片机可以利用自身的I/O口,或者是地址线扩展方法,通过地址线确定和选择双端口RAM中的指定存储单元。

3.读写信号单片机的wR和RD引脚分别和双端口RAM的左、右两套独立的读写引脚相连。单片机通过RD引脚从双端口RAM中读取相应地址存储单元的数据,通过wR引脚发出写信号,向双端口RAM中相应的存储单元中写入数据。

4.争用标志在双端口RAM中,可有一套独立的“BUSY”逻辑线,保证两个单片机对双端口RAM的同一单元读写操作的正确性。从而解决端口争用问题。

除了需要知道CY7c136的引脚定义和连线外,还需要了解单片机是如何操作双端口RAM中的数据的。单片机对双端口RAM的操作和对外部RAM操作一样。根据图1的电路连接,具体的地址定义如下://定义双端口RAM―CY7c136中的6个存储单元的地址Ox0100一Ox0600H:

#define dsyawh XBYTE【Ox0600】

#define dsyawl XBYTE[0x0100]

#define DSPitchh XBYTE【Ox0200】

#define dspitchl XBYTE[Ox0300]

#define dsrollh XBYTE[0x0400]

#define dsrolll XBYTE[Ox0500】

∥从单片机向双端口RAM―CY7C136的6个存储单元中写入3组数据:

unit numyaw=atoi(stringyaw);dsyawh=numyaw/256;dsyawl=numyaw%256;unit numpitch=atoi(stl4ngpitch);Idspitchh=numpitch/256;dspitchl=numpitch%256;unit numroll=atoi(stringroll);dsrollh=numroll/256;dsrolll=numroll%256;//主单片机从双端口RAM―CY7C136的6个存储单元中读入3组数据;读人数据后,如果原始数据是16位,则还需要将高、低位的数据叠加。

yawh=XBYTE[Ox6000];yawl=XBYTE[Ox1000];yaw=-yawh*256+yawl;pitchh=XBYTE[Ox2000];pitchl=XBYTE[Ox3000];pitch=pitchh*256+pitchl;rollh=XBYrE[Ox4000];rolll=XBYTE[0x5000];roll=rollh*256+rolll;双端口RAM在使用中数据冲突问题的解决双端口RAM在使用中应注意的一个问题就是可能发生同一数据区的争用。

当两个端口的CPU同时读取一个双端口RAM单元时,就产生了争用,会出现写入值和读取值不是所期望数据的混乱状态。通常,有4种不同的争用解决方案,分别是硬件判优方案、中断方案、令牌传递方案和软件判优方案。目前,很多双端口RAM都支持硬件判优方案,这些双端口RAM中都有片内硬件判优电路,并且两个端口上都有BUSY引脚。当出现争用现象时,双端口RAM的片内硬件判优电路确定某一个具有优先权的端口可以继续对该端口进行读写操作,对该端口而言,就像没有发生争用现象一样。硬件判优电路将另一个被延迟存取的端口的BusY引脚置为高电平,此时延迟存取端口的一方可以继续存取。硬件判优方案要求cPu能插入等待状态,所以对于具备和不具备插入等待状态的单片机就有两种不同的信号处理方法。对于具备插入等待状态功能的单片机,将双端口RAM的。BUSY连接到读端口cPu的等待状态检测线上即可。例如,对于8098单片机,可将CY7c136的一个BUSY引脚连接到8098的READY引脚即可。一般只要等待周期长度超过另一端CPU的读写周期即可保证cPu结束等待时BUSY=1。对于不具备插入等待状态的单片机,需要在电路设计和编程上使用一些技巧才能使用硬件判优方法解决争用问题。例如,对于89c 5 2单片机,由于不具备像READY之类的检测线引脚,可采用将CY7C136的一个BUSY引脚连接到89C52的P1.2引脚上来解决。89C52在读双端口RAM时,首先通过端口扫描,判断P1.2口的电平值,如果电平为高,则表示该RAM单元空闲,89C52可以执行读取数据的操作;如果此时端口电平为低,则表示该RAM单元正被另一个单片机操作,则89C52暂时停止执行读取数据的操作,等待P1.2口的电平变低,从而避免和通信单片机发生争用端口的情况。

采用上述方法解决端口争用问题的程序代码如下:

sbit moto l=Pl^2;//定义端口#define RAMTADA 1 XBYTE[Ox02001】;//定义双端口RAM的下一个单元地址//在主程序中加入如下的端口扫描程序While(!P1―21{Astring=RAMTADAl;//等到Pl.2端口的电平为低时,读取双端口RAM中的单元信息}

通过对单片机端口操作和程序的配合,有效地解决了常用单片机和双端口RAM的争用问题。实际上,利用单片机的读写时序和端口的扫描功能,是解决这类问题的常用方法。

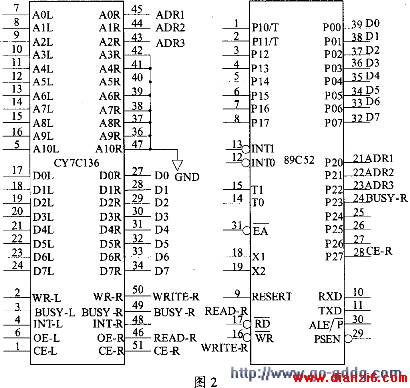

硬件电路实现图2为双端口RAM器件CY7c136与89C52的硬件连线图,鉴于篇幅有限,仅画出了CY7c136一端的连线图,以网络标号显示引脚连线。

1.数据线DOR―D7R DOR~D7R和单片机的P00-P07相连,在图中的网络标号为DO―D7,作为系统总线传输数据。

2.片选信号cY7c136的片选信号CE―R与单片机的P2.7相连,图中的网络标号为CE―R。单片机通过对P2.7的电平操作选择双端口RAM器件地址。

3.地址线AOR―A10R AOR―A10R地址线决定了CY7c136内部2K存储单元的地址。本文中只是用了6个字节的存储单元,所以只用3根地址线AOR、A1R及A2R,分别和单片机的P2.0、P2.1及P2.2相连。单片机通过这3根线选择CY7C136内部存储单元的地址。图中的网络标号为ADRl、ADR2及ADR3。

4.读写信号wR―R和OE―R WR―R和OE―R分别和单片机的wR和RD相连,单片机通过RD引脚从双端口RAM中读取相应地址存储单元的数据,通过wR引脚发出写信号,向双端口RAM中相应地址存储单元写入需要保存的数据。图中的网络标号分别为wRITE―R和READ―R。

5.争用标志BUSY―R BusY―R和单片机的P2.3相连,通过软件实现硬件判优过程。

程序设计程序的功能是实现从单片机和主单片机之间的数据共享,以及外设向双端口RAM中写人数据。外设通过RS-232串口和从单片机连接。

1.程序中的变量及说明numberyaw、numberpitch及numberroll别为外设数据1、外设数据2及外设数据3。dsyawh、dsyawl分别为外设数据1的高8位和低8位;dspitchh、dspitchl分别为外设数据2的高8位和低8位;dsrollh、dsrolll分别为外设数据3的高8位和低8位。

2.从单片机程序代码(略)

3.主单片机程序代码(略)

结束语双端口RAM器件具有通信速度快、传输质量可靠及硬件连接简单等优点,解决了以往通过串口传输数据的缺陷,是理想的接口器件。

如果觉得 双端口RAM方式的数据通讯这篇文章不错,可以推荐给朋友分享哦。 温馨提示; 本站的资料全部免费下载,为方便下次找到本站记得将本站加入收藏夹哦,牢记网址http://www.dianzi6.com

温馨提示; 本站的资料全部免费下载,为方便下次找到本站记得将本站加入收藏夹哦,牢记网址http://www.dianzi6.com|

此页提供双端口RAM方式的数据通讯学习园地, 维修教程知识 - 电路学习参考。本站还有更多的电路学习相关资料分享。

Copyright© www.dianzi6.com Inc. All rights reserved 。 1 2 3 4 5 6 7 8 |

|